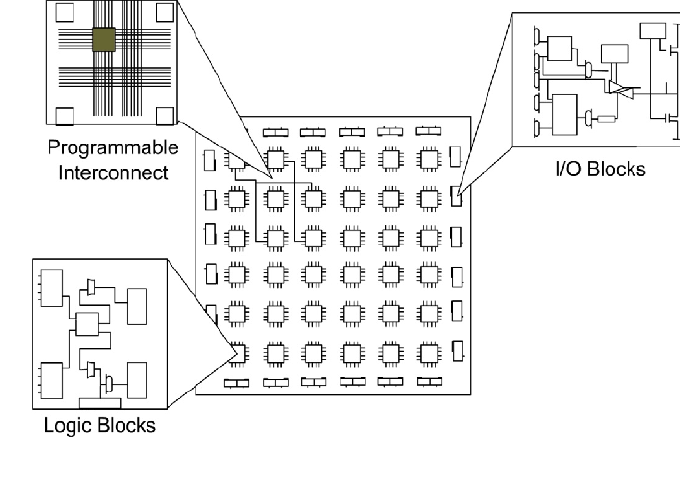

Architecture interne d'un FPGA

LUTs, bascules, blocs RAM, DSP, interconnexions — les ressources physiques d'un FPGA moderne.

Qu'est-ce qu'un FPGA ?

Un FPGA (Field-Programmable Gate Array) est un circuit intégré dont la logique est reconfigurable après fabrication. Contrairement à un ASIC (circuit figé), un FPGA peut être reprogrammé autant de fois que nécessaire.

Les ressources principales

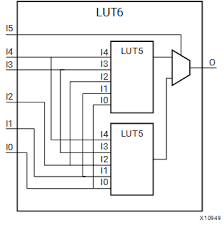

LUT — Look-Up Table

La brique de base de la logique configurable. Une LUT est une petite mémoire qui implémente n'importe quelle fonction logique.

Une LUT-6 (6 entrées, standard Xilinx 7-series) peut réaliser n'importe quelle fonction de 6 variables → 2⁶ = 64 cases mémoire.

| Paramètre | Xilinx 7-series | Intel Cyclone V |

|---|---|---|

| LUT | LUT-6 | LUT-6 (ALM) |

| LUTs / CLB | 8 | 10 / ALM |

| Nombre typique | 13k – 2M | 25k – 300k |

Bascule D (Flip-Flop)

Chaque LUT est associée à une ou plusieurs bascules D. Elles stockent l'état entre les cycles d'horloge.

Un CLB (Configurable Logic Block) contient généralement 8 LUTs + 16 bascules.

Carry Chain

Les CLBs disposent de chaînes de propagation de retenue rapide, permettant d'implémenter des additionneurs et compteurs haute performance.

BRAM — Block RAM

La mémoire embarquée dans le FPGA. Organisée en blocs de taille fixe (typiquement 18 kbits ou 36 kbits).

-- Inférence automatique d'une BRAM simple port

architecture rtl of bram_sp is

type t_mem is array(0 to 255) of std_logic_vector(7 downto 0);

signal r_mem : t_mem;

begin

process(i_clk)

begin

if rising_edge(i_clk) then

if i_we = '1' then

r_mem(to_integer(unsigned(i_addr))) <= i_data;

end if;

o_data <= r_mem(to_integer(unsigned(i_addr)));

end if;

end process;

end architecture rtl;| Paramètre | Valeur typique |

|---|---|

| Taille d'un bloc | 18 kbits ou 36 kbits |

| Nombre de blocs | 100 – 2000 |

| Modes | Simple port, dual port, true dual port |

| Latence | 1 cycle |

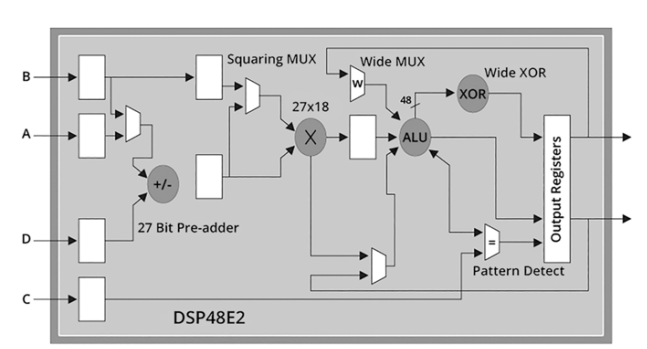

DSP — Digital Signal Processing

Blocs matériels dédiés aux multiplications et opérations MAC (Multiply-Accumulate).

Un bloc DSP48 (Xilinx) réalise : P = A × - + C en 1 cycle, à haute fréquence.

Usage typique :

- Filtres numériques (FIR, IIR)

- Corrélateurs, FFT

- Unités de traitement d'images

Le synthétiseur infère automatiquement les DSP depuis votre VHDL si la structure correspond.

I/O — Entrées/Sorties

Les broches d'un FPGA sont des I/O configurables :

| Standard | Usage |

|---|---|

| LVCMOS 3.3V / 1.8V | GPIO général |

| LVDS | Différentiel haute vitesse |

| SSTL | DDR mémoires |

| SERDES | Très haute vitesse (HDMI, PCIe) |

-- Contrainte de placement (fichier XDC Xilinx)

set_property PACKAGE_PIN W5 [get_ports o_led]

set_property IOSTANDARD LVCMOS33 [get_ports o_led]Interconnexions

Les ressources sont reliées par un réseau d'interconnexions programmables. C'est souvent le facteur limitant la fréquence maximale.

Le synthétiseur choisit les chemins de routage — c'est pourquoi une même description VHDL peut avoir des performances différentes selon le FPGA ou les contraintes.

Familles de FPGAs courants

| Fabricant | Famille | Cible |

|---|---|---|

| Xilinx (AMD) | Artix-7, Kintex-7 | Mid-range |

| Xilinx (AMD) | Zynq-7000 | SoC (ARM + FPGA) |

| Xilinx (AMD) | Virtex Ultrascale+ | Hautes performances |

| Intel (Altera) | Cyclone V / 10 | Low-cost |

| Intel (Altera) | Arria 10 | Mid-range |

| Lattice | ECP5 | Ultra low-power |

| Gowin | GW1N | Bas coût, hobbyistes |