Analyse Statique de Timing (STA)

Comprendre le setup time, le hold time, le chemin critique et le calcul de slack en FPGA.

Qu'est-ce que la STA ?

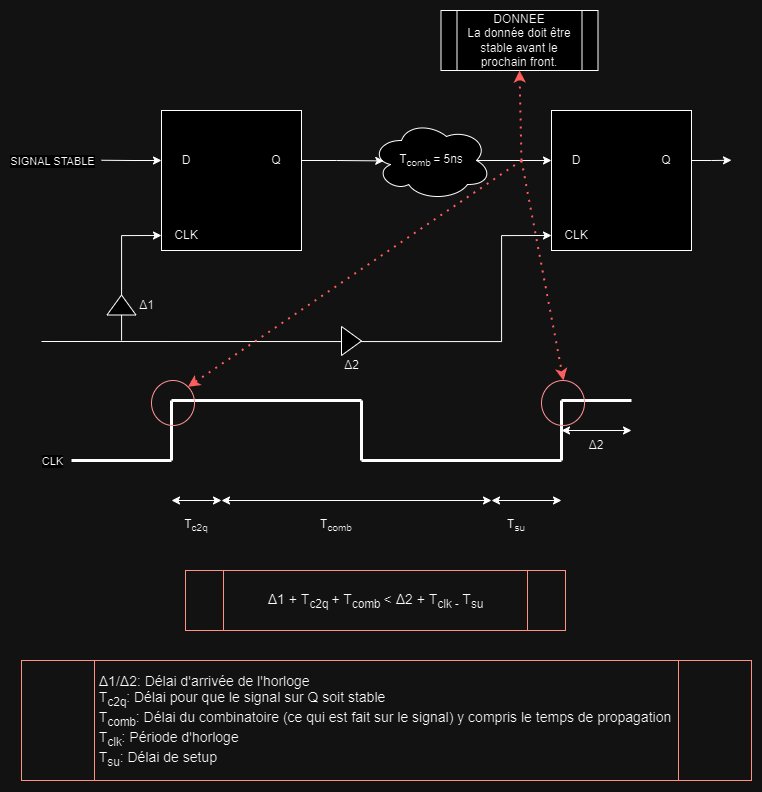

L'Analyse Statique de Timing (Static Timing Analysis) est une méthode utilisée pour évaluer le comportement temporel d'un circuit sans le simuler en détail. Elle examine les chemins critiques — les chemins où les signaux doivent respecter des contraintes de temps strictes pour garantir le bon fonctionnement.

Ces contraintes incluent :

- Les délais d'horloge

- Les temps de propagation des signaux

- Les paramètres de synchronisation (setup, hold)

La STA permet de détecter les violations de timing avant même de programmer le FPGA.

Setup Time et Hold Time

Setup Time

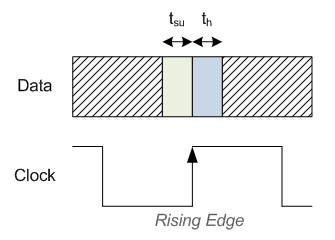

Le setup time est la durée pendant laquelle les données doivent être stables avant le front d'horloge pour être correctement capturées par une bascule.

Si les données arrivent trop tard (violation de setup), la bascule capturera une valeur incorrecte ou indéfinie.

Hold Time

Le hold time est la durée pendant laquelle les données doivent rester stables après le front d'horloge pour garantir leur capture correcte.

Si les données changent trop tôt après le front (violation de hold), la bascule peut capturer une valeur erronée.

Calcul de la Slack

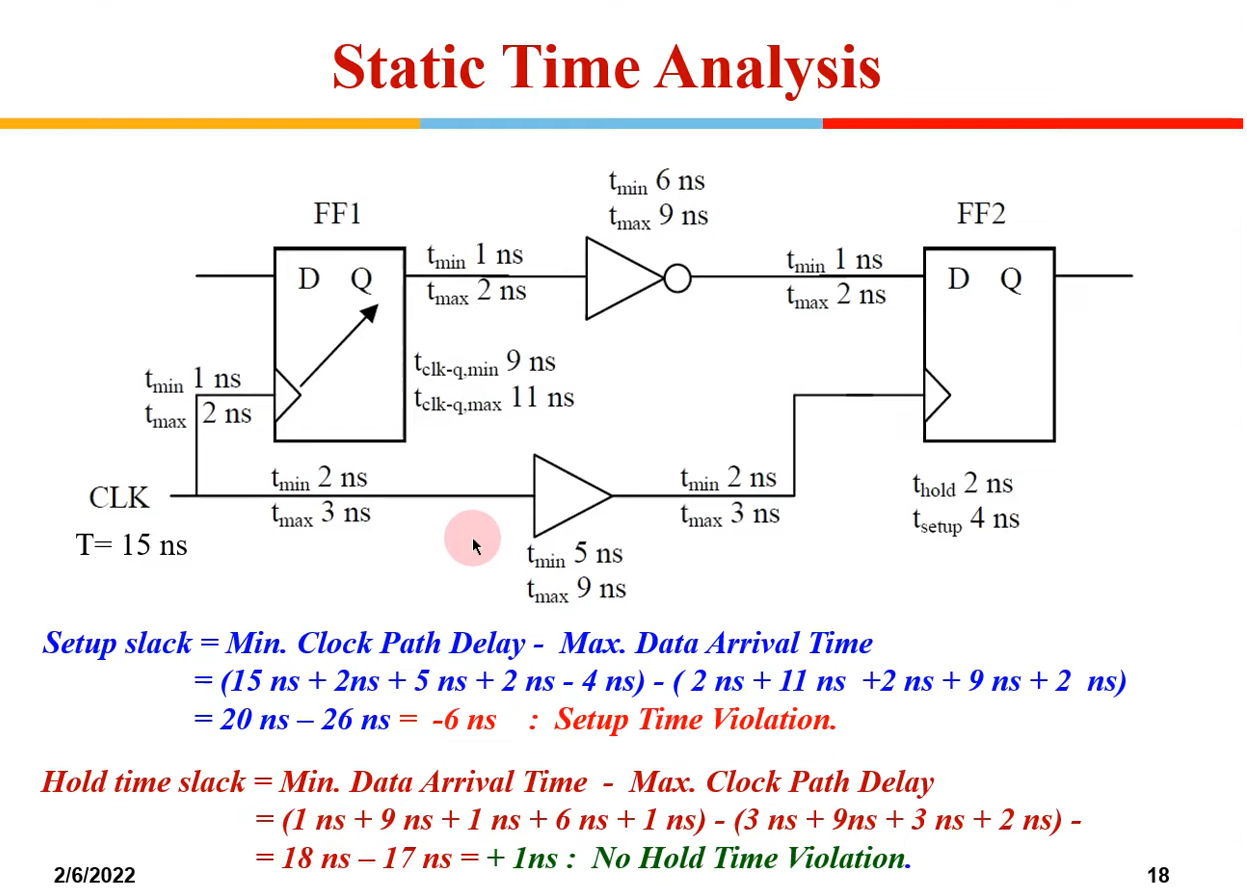

La slack est la marge temporelle calculée. Une slack positive indique que le timing est respecté, une slack négative indique une violation.

Slack de Setup

Setup Slack = Tdata,max − Tclock,min

On soustrait la somme des délais minimum du chemin d'horloge à la somme des temps d'arrivée maximaux de la donnée.

Dans l'exemple ci-dessus : −6 ns → violation de setup. Il faut réduire la fréquence ou optimiser le chemin.

Slack de Hold

Hold Slack = Tdata,min − Tclock,max

On soustrait la somme des délais maximum du chemin d'horloge à la somme des temps d'arrivée minimaux de la donnée.

Dans l'exemple ci-dessus : +1 ns → pas de violation.

Ce que font les outils modernes

Les outils comme Vivado calculent automatiquement toutes ces marges après la phase d'implémentation (placement & routage). Le rapport de timing indique :

| Rapport | Description |

|---|---|

| WNS (Worst Negative Slack) | Pire marge de setup — doit être ≥ 0 |

| WHS (Worst Hold Slack) | Pire marge de hold — doit être ≥ 0 |

| TNS (Total Negative Slack) | Somme de toutes les violations de setup |

| THS (Total Hold Slack) | Somme de toutes les violations de hold |

Il est important de savoir lire et interpréter ces rapports, même si Vivado les génère automatiquement. Une erreur de timing non corrigée peut provoquer des comportements aléatoires sur le FPGA.