Block Design & IPs

Utiliser les blocs design Vivado et les IPs propriétaires pour créer des designs SoC sur FPGA.

Qu'est-ce qu'un block design ?

Le block design est une autre façon de développer sur FPGA. En plus du VHDL, vous pouvez assembler visuellement des IPs (Intellectual Properties) — des blocs fonctionnels fournis par le fabricant ou créés par vos soins — et les connecter graphiquement.

Les avantages principaux :

- Connecter les protocoles propriétaires (AXI, etc.) de façon simple et visuelle

- Utiliser des IPs optimisées par le fabricant (mémoires, processeurs, contrôleurs)

- Faciliter les connexions entre blocs dans les conceptions SoC

Les block designs sont particulièrement utiles dès qu'on utilise un SoC. Pour exploiter la partie CPU, on utilise les blocs fournis par le fabricant pour communiquer avec les mémoires et le processeur depuis le FPGA.

Tutoriel pas à pas — ZYNQ Z2

Pour illustrer le fonctionnement, nous allons créer un exemple simple : faire clignoter des LEDs à l'aide de boutons sur une carte ZYNQ Z2.

Cela nous permettra de voir :

- Comment utilise-t-on les IPs ?

- Comment fonctionne une carte SoC ?

Étape 1 & 2 — Créer le projet Vivado

Créez votre projet Vivado en sélectionnant votre carte cible. Reportez-vous au cours Premier projet Vivado si nécessaire.

Étape 3 — Créer le block design

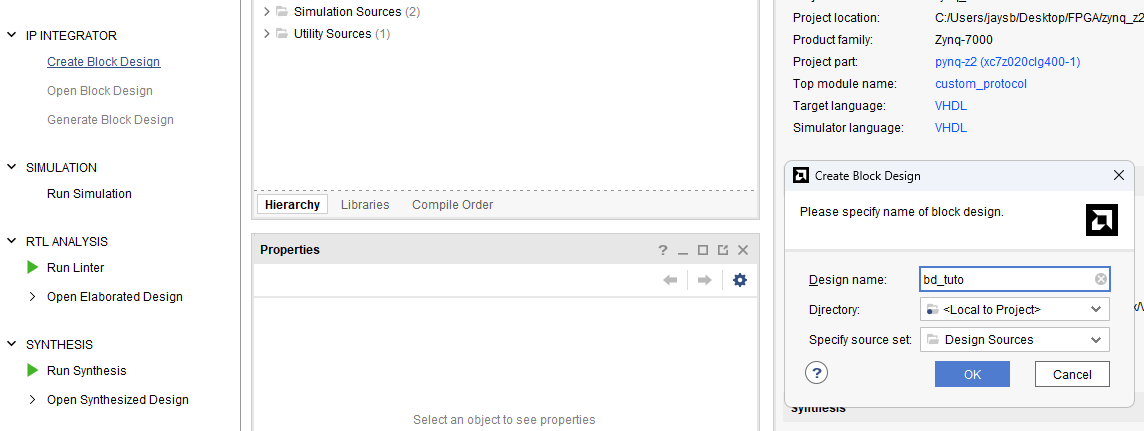

Cliquez sur "Create block design" et donnez-lui un nom (par exemple bd).

Étape 4 — Ajouter le Processing System

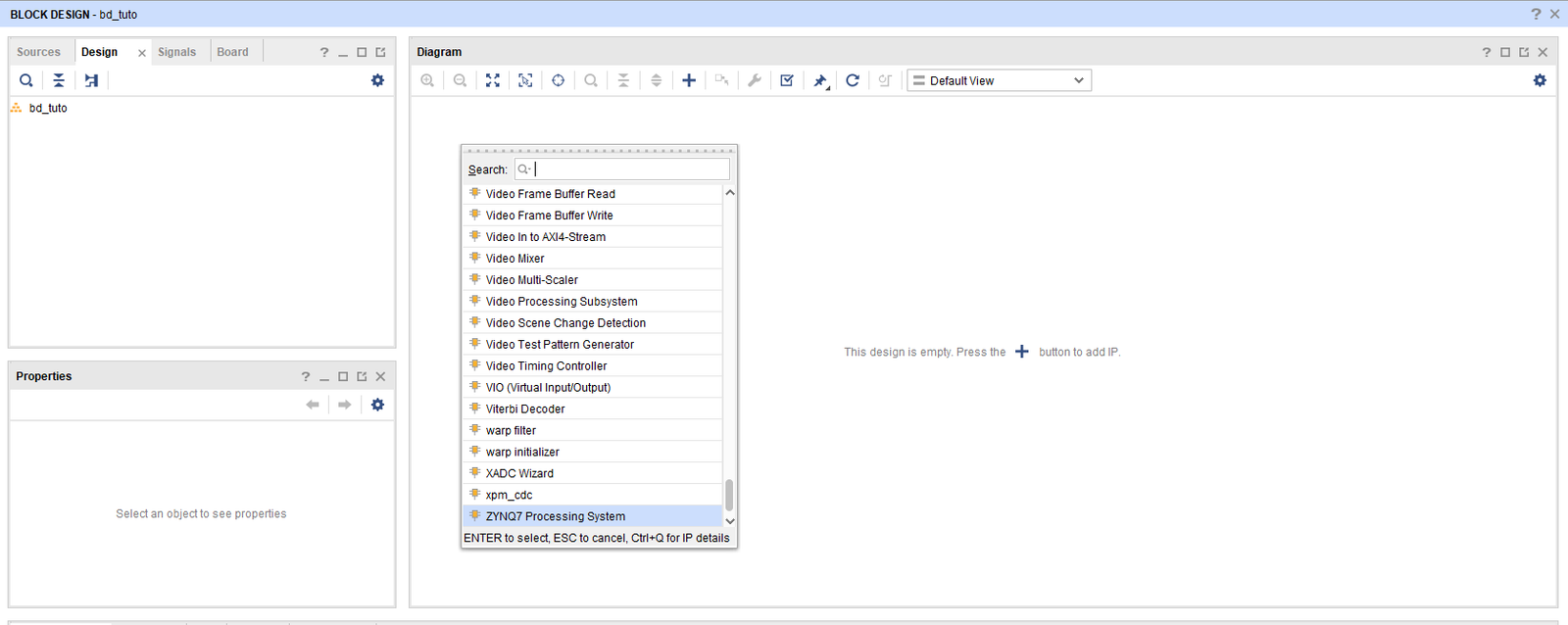

Vous arrivez sur une page permettant d'ajouter des IPs. Cherchez et ajoutez le "Processing System" correspondant à votre carte (Zynq7 Processing System pour la ZYNQ Z2).

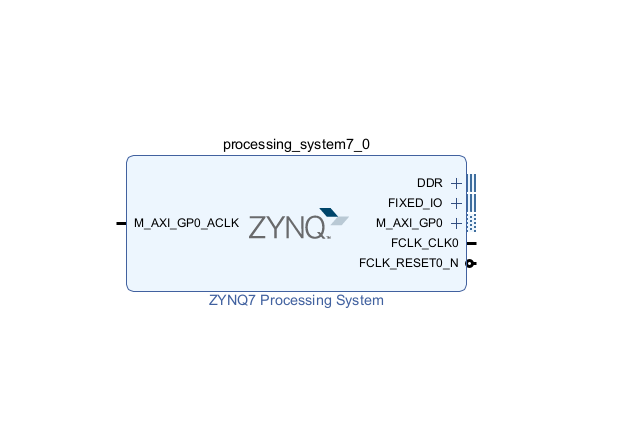

Vous devriez obtenir ce résultat :

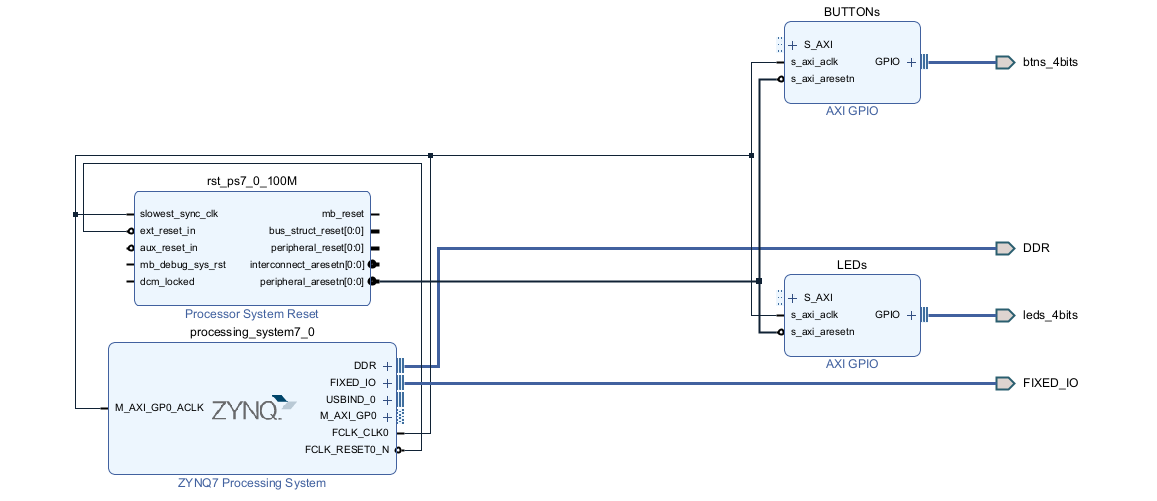

Étape 5 — Ajouter les IPs GPIO

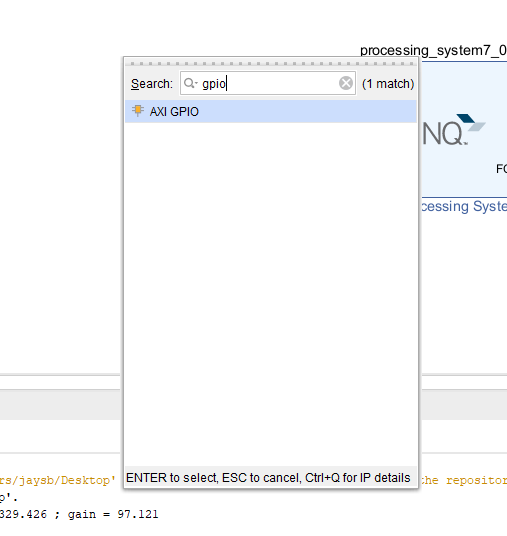

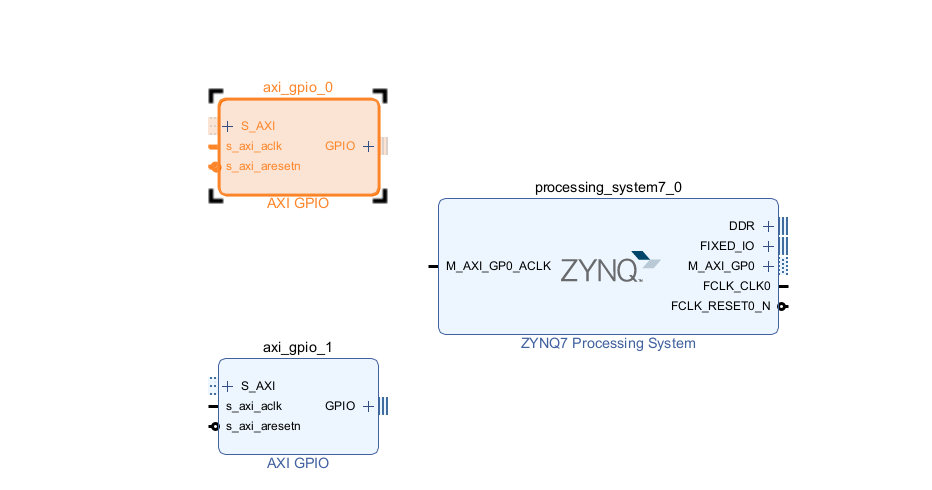

Faites clic droit → Add IP et cherchez GPIO. Ajoutez-en deux : une pour les LEDs, une pour les boutons.

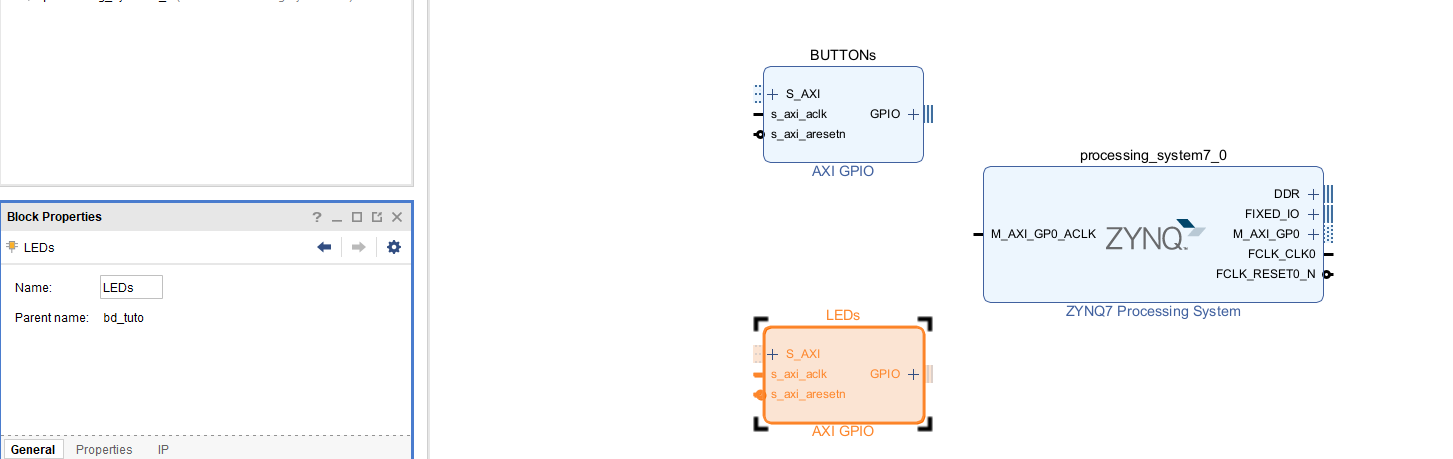

Dans l'onglet Block Properties, renommez les blocs LEDs et BUTTONs pour plus de clarté.

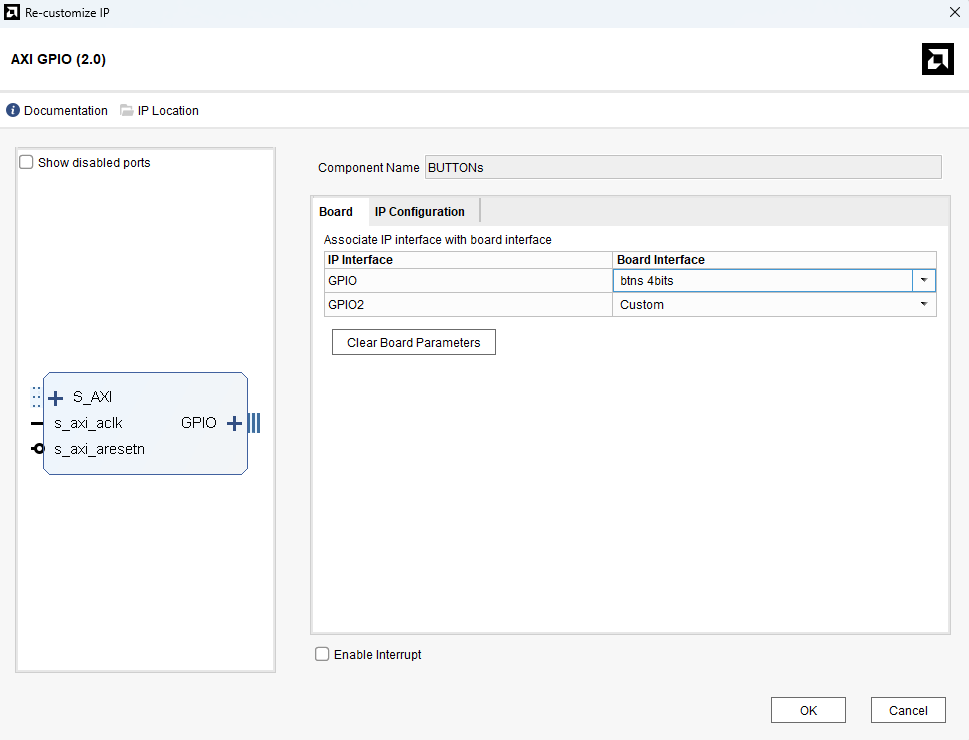

Configurez ensuite les entrées/sorties de chaque IP. Pour BUTTONs, sélectionnez btns_4bits. N'hésitez pas à supprimer les sorties générées automatiquement et à relancer "Run Connection Automation".

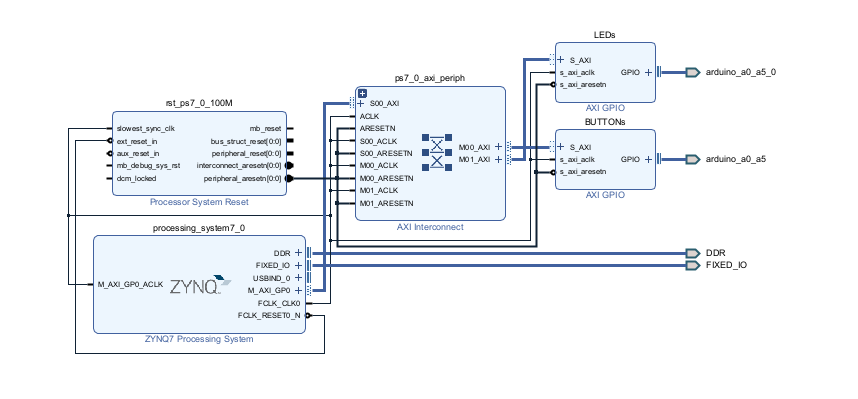

Étape 6 — Connexion automatique

Cliquez sur "Run Block Automation" puis "Run Connection Automation" en sélectionnant tout. Vivado va connecter automatiquement les blocs.

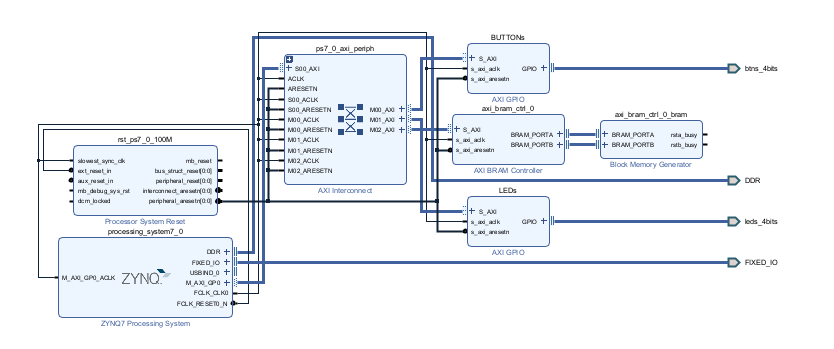

Étape 7 — Ajouter une mémoire AXI BRAM

Pour permettre au CPU d'accéder aux LEDs et boutons, il lui faut une mémoire AXI. Ajoutez une IP AXI BRAM Controller et relancez l'étape 6.

Étape 8 — Créer sa propre IP

Notre objectif final est de créer une IP personnalisée pour connecter directement les LEDs aux boutons. Supprimez ce qui est inutile.

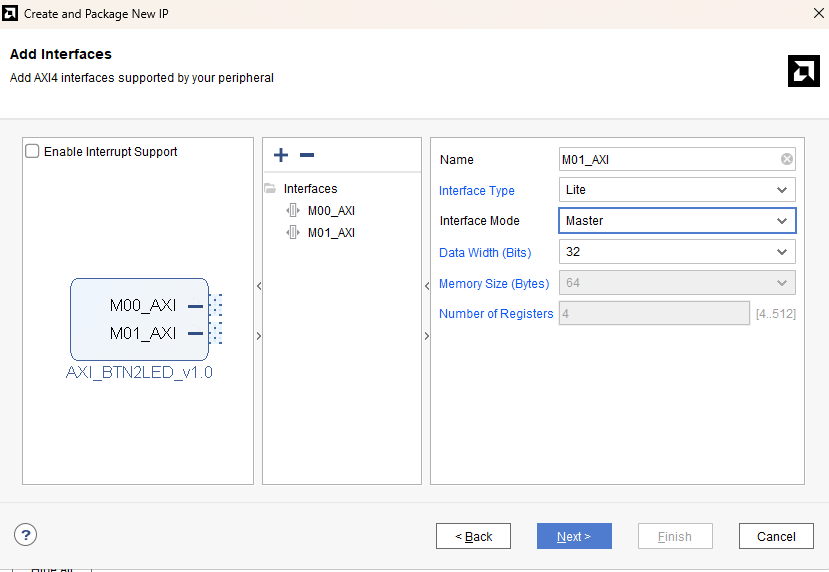

Étape 9 & 10 — Créer et packager l'IP

Allez dans Tools → Create and Package new IP. Choisissez une interface AXI-Lite Master (la même que les AXI GPIO). Ajoutez-en deux : une pour les LEDs, une pour les boutons. À la dernière page, cliquez sur "Edit IP".

À retenir

| Concept | Description |

|---|---|

| IP | Bloc fonctionnel réutilisable (fourni ou custom) |

| Processing System | La partie CPU du SoC (Zynq) |

| AXI GPIO | IP permettant de contrôler des GPIO via le bus AXI |

| AXI BRAM | Mémoire accessible par le CPU via AXI |

| Run Connection Automation | Vivado connecte automatiquement les blocs compatibles |

Pour aller plus loin, la compréhension des protocoles AXI est indispensable. Consultez le cours Protocole AXI.