Du code VHDL au hardware

Comment votre code VHDL se transforme en hardware FPGA : synthèse, implémentation et bitstream.

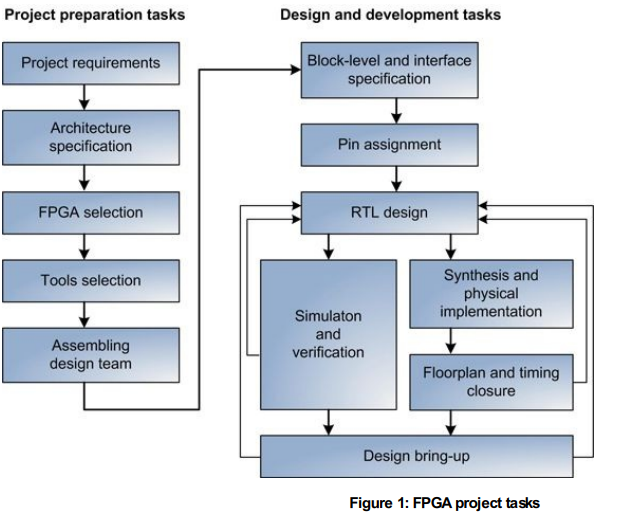

Le flot de conception complet

Étape 1 : Synthèse

La synthèse traduit votre VHDL en un réseau de portes logiques (netlist).

Ce que le synthétiseur fait

| Construction VHDL | Hardware inféré |

|---|---|

AND, OR, NOT | Portes logiques dans LUTs |

if rising_edge(i_clk) | Bascule D |

case sur signal | MUX ou LUT |

array de signaux | Registres ou BRAM |

* (multiplication) | DSP ou LUTs |

when/select | MUX |

Exemple

-- Code VHDL

o_y <= (i_a AND i_b) OR (NOT i_c);Sera synthétisé en une LUT-3 avec la table de vérité appropriée.

-- Code VHDL

process(i_clk)

begin

if rising_edge(i_clk) then

r_data <= i_data;

end if;

end process;Sera synthétisé en une bascule D avec i_data sur l'entrée D et r_data sur Q.

Étape 2 : Mapping technologique

La netlist abstraite est mappée sur les ressources physiques du FPGA cible.

Le synthétiseur choisit d'utiliser :

- Des LUTs pour la logique combinatoire

- Des bascules D pour la logique registrée

- Des BRAM pour les mémoires (si la taille est suffisante)

- Des DSP pour les multiplications

Vous pouvez influencer ces choix avec des attributs de synthèse :

-- Forcer en BRAM (Xilinx)

attribute ram_style : string;

attribute ram_style of r_mem : signal is "block";

-- Forcer en registres distribués

attribute ram_style of r_mem : signal is "distributed";Étape 3 : Placement

Les ressources logiques sont assignées à des positions physiques sur le FPGA.

Le placement influence :

- La fréquence maximale (signaux longs = lents)

- La consommation en puissance

- L'utilisation des ressources

Vous pouvez contraindre le placement pour des raisons de timing :

# Contrainte de placement (Xilinx XDC)

set_property LOC SLICE_X0Y0 [get_cells r_counter_reg[0]]Étape 4 : Routage

Les interconnexions entre les ressources placées sont configurées.

Le routage est souvent le goulot d'étranglement en timing. Des signaux qui traversent beaucoup de ressources d'interconnexion introduisent des délais.

Analyse du timing (STA)

L'outil effectue une analyse statique du timing pour vérifier que tous les chemins respectent les contraintes.

Chemin de données :

FF_src → [combo logic + routage] → FF_dst

Setup time violation si :

Tclk_to_Q + T_logic + T_route > Tperiode - TsetupÉtape 5 : Bitstream

Le bitstream est le fichier de configuration qui programme le FPGA.

# Xilinx : fichier .bit

vivado -mode batch -source program.tcl

# Intel : fichier .sof / .rbf

quartus_pgm -m jtag -o "p;output.sof@1"Types de mémoire de configuration

| Type | Persistance | Usage |

|---|---|---|

| SRAM interne | Volatile (perdu au reset) | Développement |

| Flash externe | Non volatile | Production |

| EEPROM | Non volatile | Petits FPGAs |

Sur la plupart des kits de développement, la configuration SRAM est chargée via JTAG depuis l'outil de synthèse. Pour la production, on utilise une Flash SPI externe.

Ce que VHDL ne peut PAS synthétiser

| Construction | Simulation | Synthèse |

|---|---|---|

wait for 10 ns | ✓ | ✗ |

Types réels (real, float) | ✓ | ✗ par-iellement |

Fichiers (textio) | ✓ | ✗ |

assert | ✓ | ✗ (i-noré) |

after dans affectation | ✓ | ✗ |

Bonnes pratiques pour la synthèse

- Tester en simulation d'abord — ne pas synthétiser du code non simulé

- Respecter les templates — bascule D, RAM, FSM (le synthétiseur les reconnaît)

- Éviter les latches — utiliser des valeurs par défaut dans les process combinatoires

- Contraindre le timing — fichier SDC/XDC avec

create_clock - Vérifier les rapports —

Timing Summary,Utilization,Synthesis Log

# Contrainte d'horloge minimale (Xilinx XDC)

create_clock -period 10.000 -name sys_clk [get_ports i_clk]