Introduction au VHDL

Qu'est-ce que le VHDL, son histoire, et pourquoi l'utiliser pour les FPGAs ?

Qu'est-ce que le VHDL ?

VHDL (VHSIC Hardware Description Language) est un langage de description matérielle (HDL) standardisé IEEE. Il permet de décrire le comportement et la structure des circuits numériques.

VHSIC = Very High Speed Integrated Circuits — programme de recherche américain des années 1980.

Le VHDL est utilisé pour :

- Modéliser et simuler des circuits numériques

- Synthétiser du code vers du matériel réel (FPGA, ASIC)

- Documenter et vérifier l'architecture d'un système numérique

Historique

| Année | Événement |

|---|---|

| 1983 | Création par le DOD (Département de la Défense américain) |

| 1987 | Première standardisation IEEE 1076-1987 |

| 1993 | Révision majeure IEEE 1076-1993 (VHDL-93) |

| 2008 | VHDL-2008 : ajout des types non signés, IEEE numeric_std |

| 2019 | VHDL-2019 : dernière révision en vigueur |

La version la plus utilisée en industrie reste VHDL-93 / VHDL-2008.

VHDL vs Verilog

Ces deux langages dominent le marché. Voici une comparaison :

| Critère | VHDL | Verilog |

|---|---|---|

| Syntaxe | Verbeuse, typée fortement | Compacte, proche du C |

| Popularité | Europe, défense, aérospatial | USA, Asie, semiconducteurs |

| Typage | Strict (fortement typé) | Permissif |

| Standard | IEEE 1076 | IEEE 1364 / 1800 (SystemVerilog) |

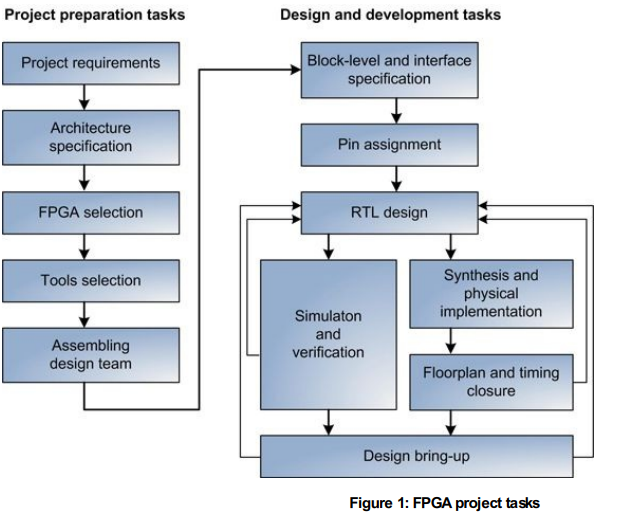

Flot de conception FPGA

- Écriture : vous décrivez le comportement en VHDL

- Simulation : vérification fonctionnelle (testbench)

- Synthèse : transformation en netlist de portes logiques

- Implémentation : placement sur les ressources physiques du FPGA

- Programmation : chargement du bitstream sur la puce

Premier aperçu du VHDL

Voici la structure minimale d'un fichier VHDL :

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity mon_circuit is

port (

i_a : in std_logic;

i_b : in std_logic;

o_y : out std_logic

);

end entity mon_circuit;

architecture rtl of mon_circuit is

begin

o_y <= i_a AND i_b;

end architecture rtl;Ce code décrit un simple ET logique à deux entrées. Nous verrons chaque partie en détail dans les prochains cours.

Points clés à retenir

- Le VHDL décrit du hardware, pas un algorithme séquentiel

- Tout ce qui est dans l'architecture s'exécute en parallèle

- Le VHDL est fortement typé : les types doivent correspondre exactement

- La simulation et la synthèse n'ont pas les mêmes contraintes