Combinatoire et Séquentiel

La distinction fondamentale entre logique combinatoire (sans mémoire) et logique séquentielle (avec horloge).

Deux types de logique numérique

En numérique, tout circuit appartient à l'une des deux catégories :

| Logique Combinatoire | Logique Séquentielle | |

|---|---|---|

| Mémoire | Non | Oui (bascules) |

| Dépend du passé | Non | Oui |

| Horloge | Non nécessaire | Indispensable |

| Exemples | Multiplexeur, additionneur | Registre, compteur, FSM |

Logique combinatoire

La sortie dépend uniquement des entrées actuelles. Pas d'état interne.

architecture rtl of mux2 is

begin

-- Affectation concurrente : immédiate, combinatoire

o_y <= i_a when i_sel = '0' else i_b;

end architecture rtl;Caractéristiques

- Pas besoin d'horloge

- Réponse instantanée (en pratique : délai de propagation)

- En synthèse : produit des LUTs (Look-Up Tables)

Logique séquentielle

La sortie dépend des entrées ET de l'état passé. Elle est synchronisée sur une horloge.

architecture rtl of registre is

signal r_data : std_logic_vector(7 downto 0);

begin

process(i_clk)

begin

if rising_edge(i_clk) then

if i_rst = '1' then

r_data <= (others => '0');

else

r_data <= i_data;

end if;

end if;

end process;

o_data <= r_data;

end architecture rtl;Caractéristiques

- Synchronisé sur le front montant (

rising_edge) ou descendant (falling_edge) - En synthèse : produit des bascules D (flip-flops)

- Le préfixe

r_indique un signal registré (voir cours 07)

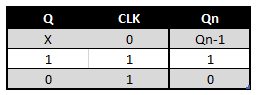

La bascule D — brique de base

La bascule D est l'élément de mémoire fondamental :

- À chaque front montant de CLK : Q prend la valeur de D

- Entre les fronts : Q conserve sa valeur précédente

process(i_clk)

begin

if rising_edge(i_clk) then

r_q <= i_d; -- bascule D simple

end if;

end process;Reset synchrone vs asynchrone

Reset synchrone (recommandé pour FPGA)

process(i_clk)

begin

if rising_edge(i_clk) then

if i_rst = '1' then

r_q <= '0'; -- reset sur le front

else

r_q <= i_d;

end if;

end if;

end process;Reset asynchrone

process(i_clk, i_rst)

begin

if i_rst = '1' then

r_q <= '0'; -- reset immédiat, sans attendre le front

elsif rising_edge(i_clk) then

r_q <= i_d;

end if;

end process;Sur FPGA, le reset synchrone est généralement préféré car il utilise les ressources de la bascule plus efficacement. Sauf contrainte particulière, utilisez le reset synchrone.

Règle des listes de sensibilité

Pour un process combinatoire : lister tous les signaux lus dans le process.

-- Combinatoire : i_a, i_b, i_sel dans la liste

process(i_a, i_b, i_sel)

begin

if i_sel = '0' then

w_y <= i_a;

else

w_y <= i_b;

end if;

end process;Pour un process séquentiel : seulement l'horloge (et le reset asynchrone si utilisé).

-- Séquentiel : uniquement i_clk

process(i_clk)

begin

if rising_edge(i_clk) then

r_q <= i_d;

end if;

end process;VHDL-2008 introduit

process(all)qui capture automatiquement tous les signaux. Pratique mais attention à la compatibilité outil.