Protocole AXI

Le protocole AXI (Advanced eXtensible Interface) d'ARM : canaux d'écriture, de lecture, burst et handshake.

Qu'est-ce que AXI ?

Le protocole AXI (Advanced eXtensible Interface) est un protocole d'interconnexion développé par ARM pour ses architectures AMBA. Il standardise les communications à haute performance entre les composants matériels d'un SoC (System on Chip).

Ses deux forces principales :

- Rapidité : conçu pour les échanges à haute fréquence

- Handshake : synchronisation fiable via des signaux

VALID/READYindépendants

AXI est décomposé en deux parties : les adresses et les données. Ce qui implique un nombre important de signaux.

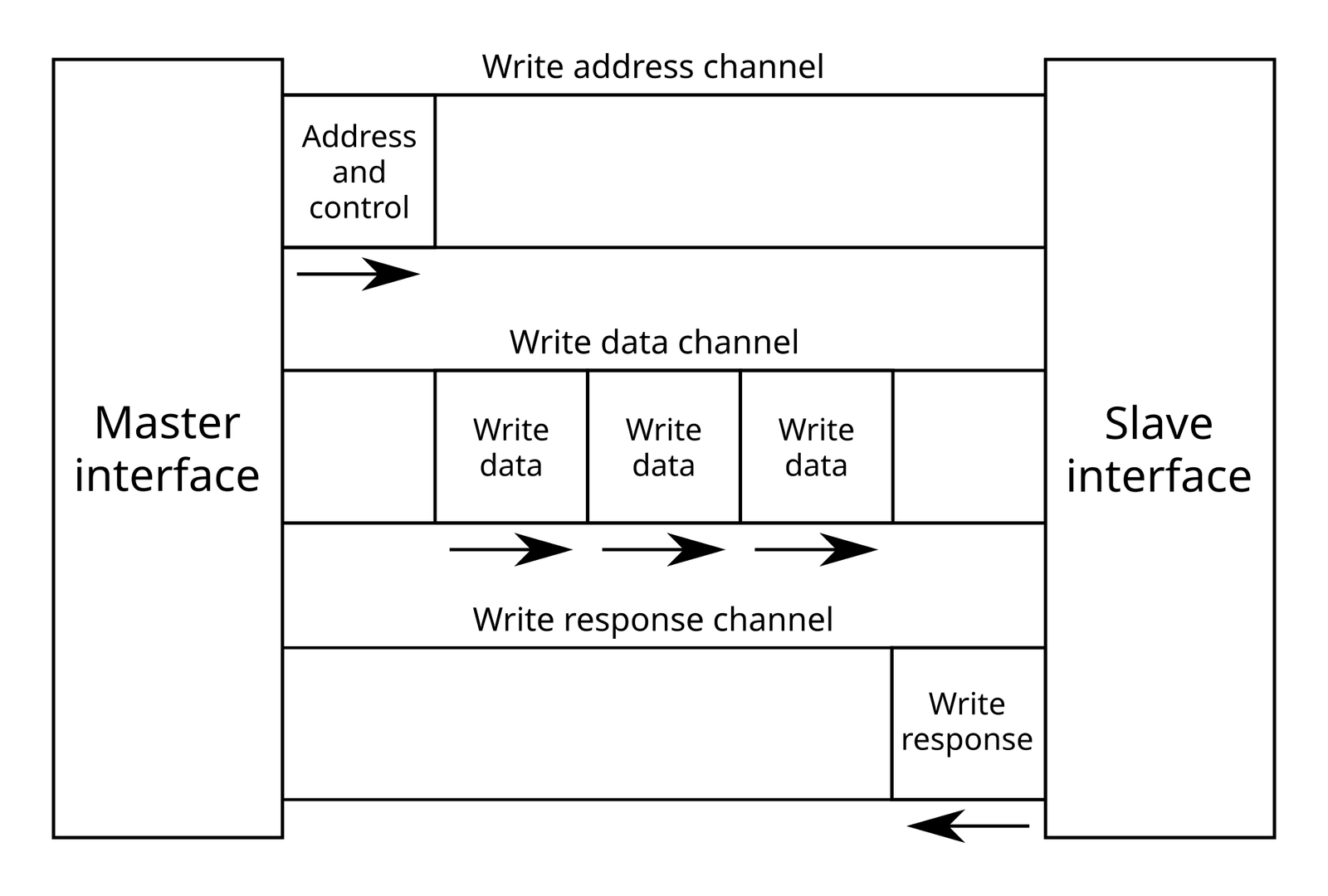

Écriture (Write)

L'écriture nécessite 13 signaux répartis sur trois canaux : adresse d'écriture (AW), données d'écriture (W) et réponse (B).

L'écriture peut se faire avec ou sans burst. Le burst consiste à envoyer une seule adresse de début, puis les données successivement — ce qui économise du temps si les adresses sont contiguës.

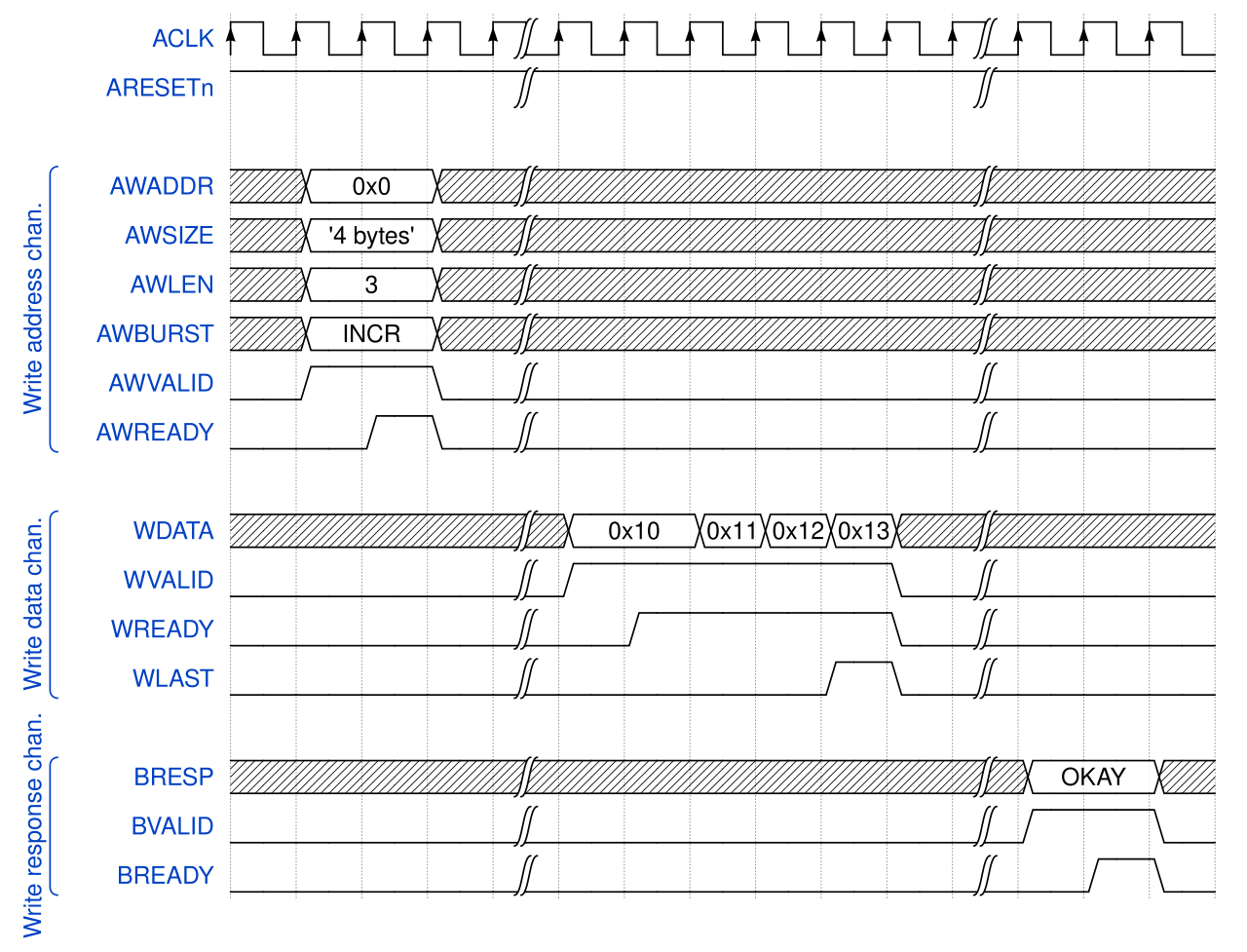

Séquence d'une transaction en écriture :

- Fixer une adresse sur AWADDR, indiquer la largeur des données (AWSIZE) et la longueur de la transaction (AWLEN).

- Fixer AWVALID en parallèle et attendre AWREADY du slave.

- Attendre WREADY et envoyer les données en burst en fixant WVALID.

- À la dernière donnée, fixer WLAST.

- Vérifier la réponse sur BRESP (valeur attendue :

OKAY).

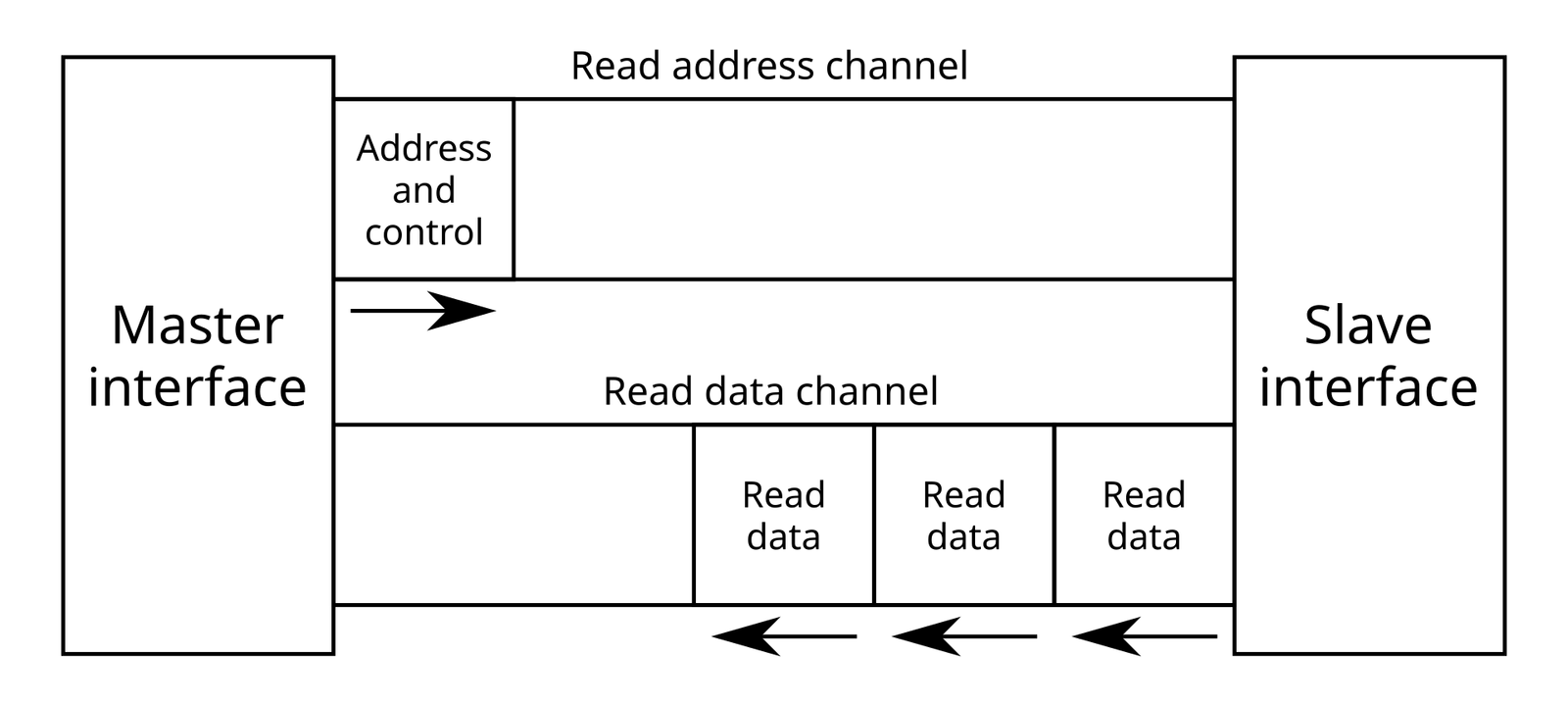

Lecture (Read)

La lecture nécessite 11 signaux répartis sur deux canaux : adresse de lecture (AR) et données de lecture (R).

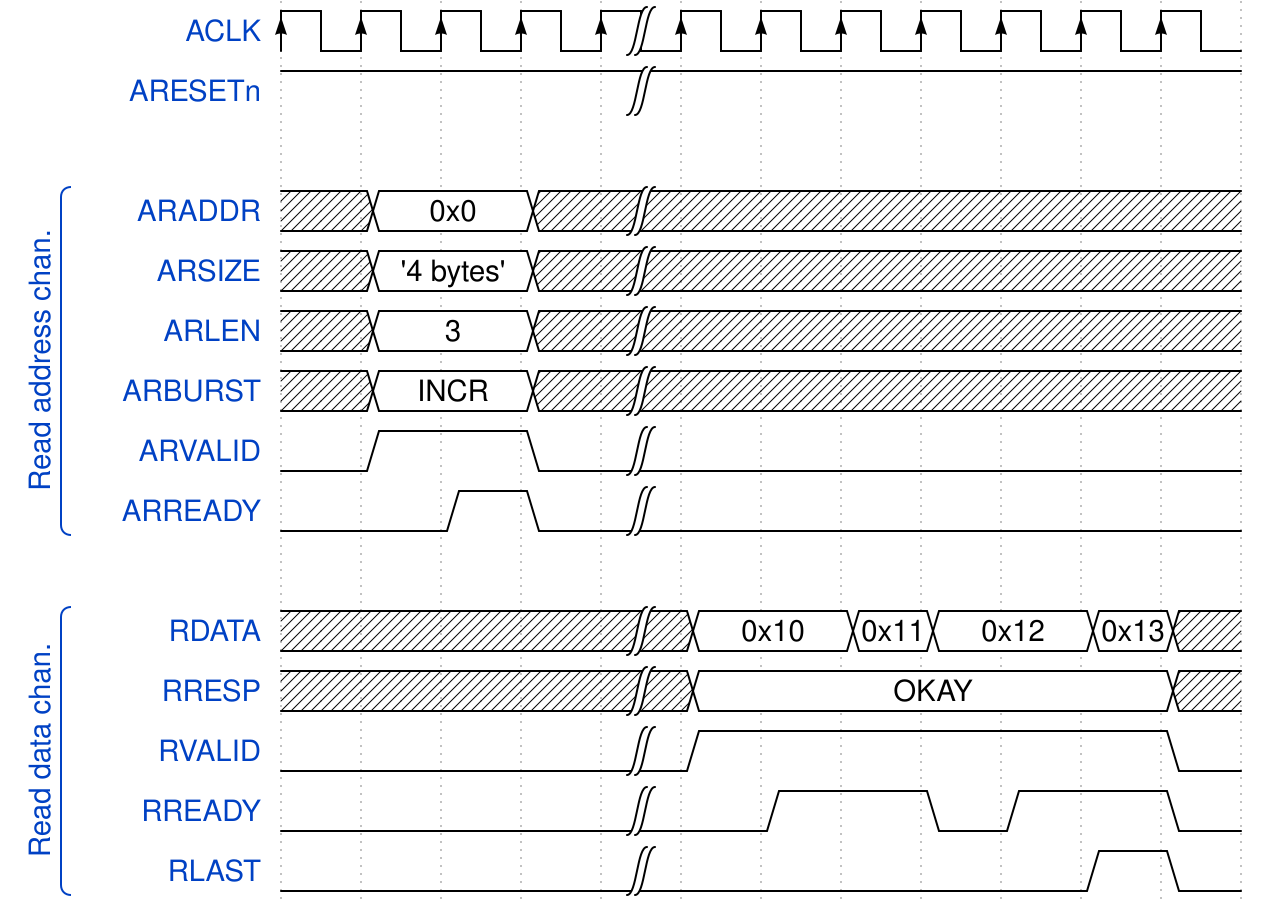

Séquence d'une transaction en lecture :

- Fixer une adresse sur ARADDR, indiquer ARSIZE et ARLEN.

- Fixer ARVALID en parallèle et attendre ARREADY du slave.

- Attendre RVALID et lire les données en burst.

- Surveiller RLAST pour détecter la dernière donnée.

- Vérifier la réponse sur RRESP (valeur attendue :

OKAY).

Récapitulatif des signaux

| Canal | Signaux principaux | Direction |

|---|---|---|

| AW (Write Address) | AWADDR, AWLEN, AWSIZE, AWVALID, AWREADY | Master → Slave |

| W (Write Data) | WDATA, WSTRB, WLAST, WVALID, WREADY | Master → Slave |

| B (Write Response) | BRESP, BVALID, BREADY | Slave → Master |

| AR (Read Address) | ARADDR, ARLEN, ARSIZE, ARVALID, ARREADY | Master → Slave |

| R (Read Data) | RDATA, RLAST, RRESP, RVALID, RREADY | Slave → Master |

Pour une version simplifiée (sans burst, sans gestion d'adresses complexes), consultez le cours Protocole AXI-Lite.