Protocole AXI-Lite

AXI-Lite : la version simplifiée d'AXI pour les registres de configuration et de contrôle.

Qu'est-ce que AXI-Lite ?

AXI-Lite est une version simplifiée du protocole AXI développée par ARM dans le cadre de l'architecture AMBA. Il est particulièrement adapté aux communications de contrôle et de configuration au sein d'un SoC.

Contrairement à AXI4 complet, AXI-Lite :

- Ne supporte pas le burst (une seule donnée par transaction)

- A une largeur de données fixe

- Utilise moins de signaux

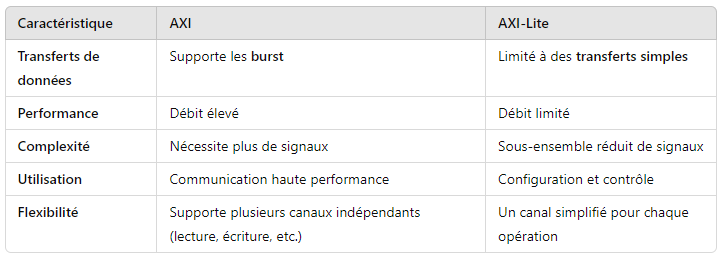

Comparaison avec AXI

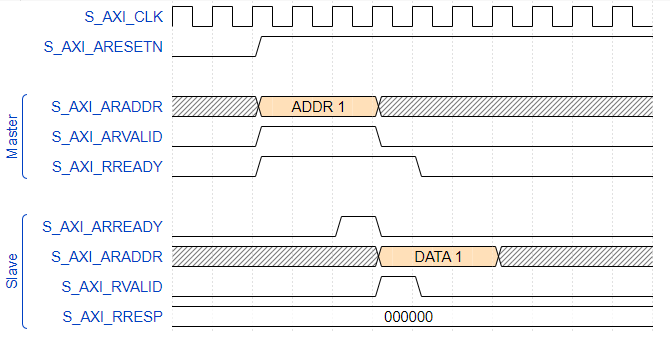

Lecture (Read)

Seulement 7 signaux sont nécessaires pour une transaction complète en lecture.

Séquence :

- Le Master attend que le Slave indique RREADY (prêt à répondre).

- Le Master place l'adresse sur ARADDR et fixe ARVALID.

- Le Slave affirme ARREADY, indiquant qu'il accepte l'adresse.

- Master et Slave remettent à zéro ARVALID et ARREADY.

- Le Slave envoie les données sur RDATA et fixe RVALID (avec RRESP en cas d'erreur).

- Au prochain front montant d'horloge (RREADY et RVALID tous deux actifs), la transaction se termine. Le Slave remet à zéro RVALID.

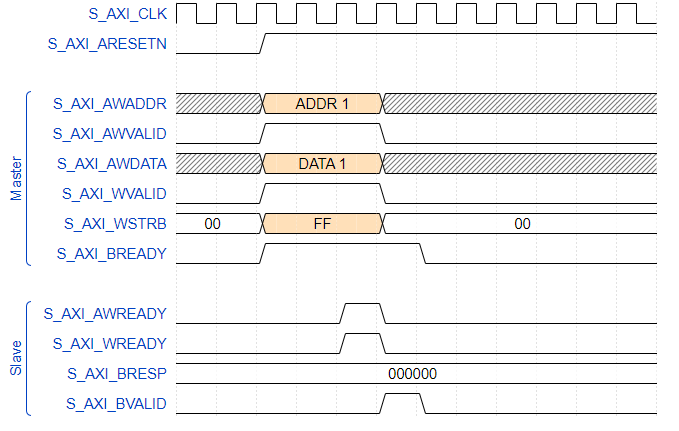

Écriture (Write)

L'écriture nécessite 10 signaux.

Séquence :

- Le Master place l'adresse sur AWADDR.

- Le Master affirme AWVALID et attend AWREADY du Slave.

- Le Master place les données sur WDATA (et le masque d'octets sur WSTRB).

- Le Master affirme WVALID et attend WREADY du Slave.

- Le Master attend la réponse BVALID du Slave.

- Le Slave fournit la réponse sur BRESP (

OKAYsi succès). - Le Master affirme BREADY pour confirmer la réception.

Récapitulatif des signaux

| Canal | Signaux | Nombre |

|---|---|---|

| Write Address | AWADDR, AWVALID, AWREADY | 3 |

| Write Data | WDATA, WSTRB, WVALID, WREADY | 4 |

| Write Response | BRESP, BVALID, BREADY | 3 |

| Read Address | ARADDR, ARVALID, ARREADY | 3 |

| Read Data | RDATA, RRESP, RVALID, RREADY | 4 |

AXI-Lite est le protocole de choix pour les registres de configuration et les périphériques simples dans un SoC Zynq.