Protocole SPI

Maîtrisez le protocole SPI (Serial Peripheral Interface) et son implémentation VHDL

Qu'est-ce que SPI ?

Le protocole SPI (Serial Peripheral Interface) est un protocole série synchrone développé par Motorola dans les années 1980. Il est très utilisé dans les systèmes embarqués pour la communication entre un microcontrôleur ou un FPGA et des périphériques comme des capteurs, des convertisseurs ADC/DAC, des mémoires Flash ou des écrans.

Ses caractéristiques principales :

- Synchrone : une horloge commune (SCK) pilote les échanges

- Full-duplex : émission et réception simultanées

- Maître/Esclave : le maître génère l'horloge et sélectionne l'esclave

- Pas d'adressage : la sélection se fait via un signal dédié SS_N

Signaux SPI

| Signal | Direction | Description |

|---|---|---|

| SCK | Maître → Esclave | Horloge série (Serial Clock) |

| MOSI | Maître → Esclave | Données maître vers esclave (Master Out Slave In) |

| MISO | Esclave → Maître | Données esclave vers maître (Master In Slave Out) |

| SS_N | Maître → Esclave | Sélection esclave, actif bas (Slave Select) |

Pour plusieurs esclaves, le maître dispose d'un signal SS_N par esclave. MOSI, MISO et SCK sont partagés (bus).

Modes SPI (CPOL / CPHA)

SPI définit 4 modes selon deux paramètres :

- CPOL (Clock Polarity) : état de repos de SCK — 0 = bas, 1 = haut

- CPHA (Clock Phase) : moment d'échantillonnage — 0 = front montant actif, 1 = front descendant actif

| Mode | CPOL | CPHA | Échantillonnage | Description |

|---|---|---|---|---|

| 0 | 0 | 0 | Front montant SCK | Repos SCK bas, échantillon sur montant |

| 1 | 0 | 1 | Front descendant SCK | Repos SCK bas, échantillon sur descendant |

| 2 | 1 | 0 | Front descendant SCK | Repos SCK haut, échantillon sur descendant |

| 3 | 1 | 1 | Front montant SCK | Repos SCK haut, échantillon sur montant |

Le mode 0 (CPOL=0, CPHA=0) est le plus courant. C'est celui utilisé dans les exercices de la plateforme.

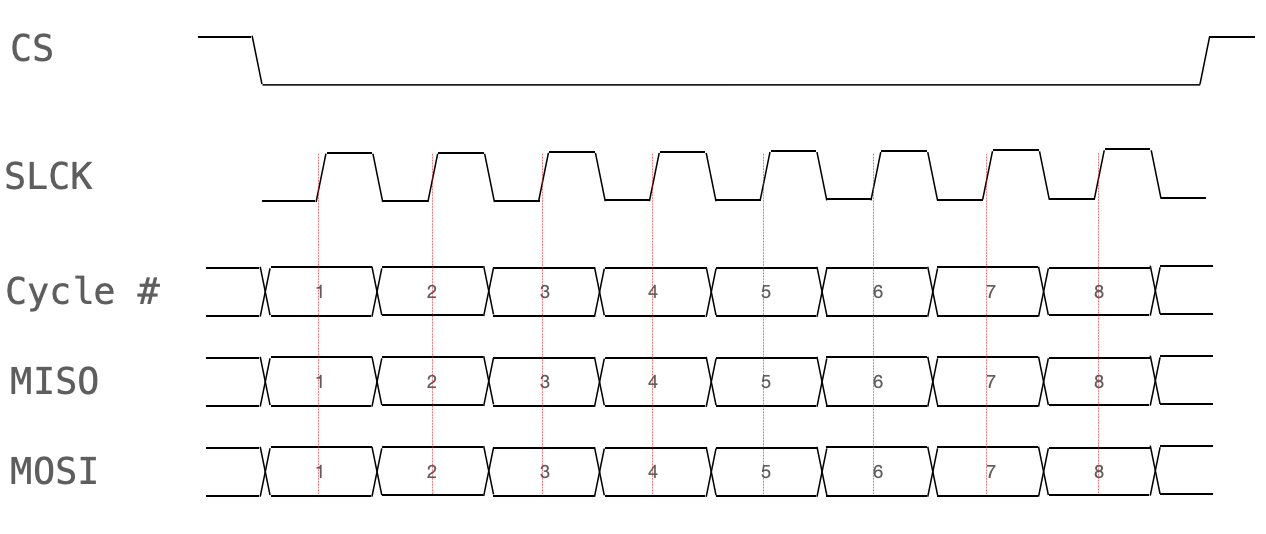

Trame SPI

Une transaction SPI se déroule ainsi :

- Le maître abaisse SS_N (actif bas) pour sélectionner l'esclave

- Le maître génère des impulsions SCK

- À chaque cycle SCK, 1 bit est transféré dans chaque direction (MOSI et MISO)

- Les données sont transmises MSB en premier (convention la plus répandue)

- Le maître remonte SS_N pour terminer la transaction

Pour une trame de 8 bits :

Implémentation VHDL

Mettez en pratique l'implémentation SPI avec les exercices suivants :

Exercices SPI disponibles :

- Esclave SPI (Mode 0) — Implémentez un récepteur SPI esclave complet avec synchronisation et détection de fronts

- Maître SPI simplifié — Construisez un contrôleur SPI maître basique

- Maître SPI Mode 0 — Maître SPI avec diviseur d'horloge configurable

- Maître SPI complet — Maître SPI avancé avec support multi-mode (avancé)

Points d'attention

- Synchronisation : les signaux SPI (SCK, SS_N, MOSI) viennent d'un domaine d'horloge externe → toujours les resynchroniser avec un double registre avant utilisation dans le domaine système

- CPOL/CPHA : vérifier le datasheet du composant esclave. Une incompatibilité de mode provoque des données corrompues sans erreur visible

- SS_N doit rester bas pendant toute la transaction. Si SS_N remonte entre deux octets, l'esclave réinitialise son compteur de bits

- Fréquence SCK : limitée par la fréquence maximale de l'esclave et le délai de propagation MISO

- Ordre des bits : MSB first est la convention standard, mais certains périphériques utilisent LSB first — vérifier la documentation

Avantages et inconvénients

| Avantages | Inconvénients |

|---|---|

| Simple à implémenter | Un fil SS_N par esclave (beaucoup de pins) |

| Haute vitesse (dizaines de MHz) | Pas d'accusé de réception (ACK) |

| Full-duplex | Distance limitée |

| Protocole flexible | Pas de détection d'erreurs native |