Protocole I2C

Maîtrisez le protocole I2C (Inter-Integrated Circuit) et ses mécanismes d'adressage et d'acquittement

Qu'est-ce que I2C ?

Le protocole I2C (Inter-Integrated Circuit, prononcé "I carré C" ou "I deux C") a été développé par Philips Semiconductors (aujourd'hui NXP) en 1982. Il permet la communication entre plusieurs composants sur un bus série à seulement deux fils.

Ses caractéristiques principales :

- 2 fils : SDA (données) et SCL (horloge)

- Open-drain : les lignes nécessitent des résistances de pull-up externes

- Multi-maître : arbitrage matériel possible entre plusieurs maîtres

- Adressage : chaque esclave possède une adresse unique (7 ou 10 bits)

- ACK/NACK : accusé de réception à chaque octet

Signaux I2C

| Signal | Type | Description |

|---|---|---|

| SDA | Open-drain bidirectionnel | Serial Data — données |

| SCL | Open-drain bidirectionnel | Serial Clock — horloge |

Les deux lignes sont tirées au niveau haut par des résistances de pull-up. Tout composant sur le bus peut abaisser une ligne (drain ouvert), mais aucun ne peut la forcer au niveau haut — seules les résistances de pull-up le font.

Conditions Start et Stop

I2C utilise deux conditions spéciales qui ne respectent pas les transitions normales (données stables pendant SCL haut) :

Condition START : SDA descend pendant que SCL est haut. Condition STOP : SDA monte pendant que SCL est haut.

Les données sur SDA ne doivent changer que lorsque SCL est bas — sauf pour les conditions START et STOP.

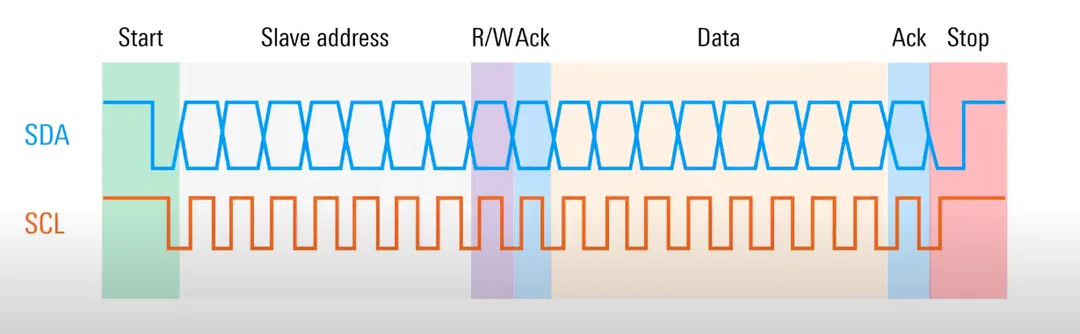

Trame I2C

Une transaction I2C typique (écriture) :

START | Adresse (7 bits) | R/W='0' | ACK | Data byte | ACK | STOP- START : initié par le maître

- Adresse : 7 bits MSB en premier, identifie l'esclave cible

- R/W bit : 0 = écriture (maître → esclave), 1 = lecture (esclave → maître)

- ACK : l'esclave tire SDA bas pour acquitter

- Données : octets transmis, chacun suivi d'un ACK/NACK

- STOP : initié par le maître pour libérer le bus

ACK et NACK

Après chaque octet de 8 bits, le récepteur envoie :

- ACK (Acknowledge) : SDA bas pendant le 9e coup d'horloge — réception correcte

- NACK (Not Acknowledge) : SDA haut (relâché) — erreur ou fin de lecture

En lecture, le maître envoie un NACK après le dernier octet pour signaler qu'il n'en veut plus.

Implémentation VHDL — Machine à états maître I2C

library ieee;

use ieee.std_logic_1164.all;

entity i2c_master is

generic (

g_SYS_CLK_HZ : positive := 100_000_000; -- 100 MHz

g_I2C_CLK_HZ : positive := 400_000 -- 400 kHz (Fast mode)

);

port (

i_clk : in std_logic;

i_rst : in std_logic;

i_start : in std_logic;

i_rw : in std_logic; -- '0'=write, '1'=read

i_addr : in std_logic_vector(6 downto 0);

i_data : in std_logic_vector(7 downto 0);

o_data : out std_logic_vector(7 downto 0);

o_busy : out std_logic;

o_ack_err : out std_logic;

io_sda : inout std_logic;

io_scl : inout std_logic

);

end entity i2c_master;La machine à états typique comprend les états :

IDLE→START→ADDR→ACK_ADDR→DATA→ACK_DATA→STOP

L'implémentation complète est disponible dans l'exercice correspondant.

Clock Stretching

L'esclave peut "étirer" SCL en le maintenant bas pour ralentir le maître. Le maître doit surveiller SCL et attendre qu'il remonte avant de continuer.

Cette fonctionnalité nécessite que SCL soit aussi open-drain (bidirectionnel).

Arbitrage multi-maître

Si deux maîtres démarrent une transaction simultanément, l'arbitrage est résolu automatiquement :

- Chaque maître compare la valeur qu'il émet sur SDA avec ce qu'il lit

- Si un maître émet '1' mais lit '0', il a perdu l'arbitrage et cesse d'émettre

- Le maître "gagnant" continue sans interruption

Vitesses standardisées

| Mode | Vitesse max |

|---|---|

| Standard Mode | 100 kbps |

| Fast Mode | 400 kbps |

| Fast Mode Plus | 1 Mbps |

| High Speed Mode | 3,4 Mbps |

Avantages et inconvénients

| Avantages | Inconvénients |

|---|---|

| Seulement 2 fils | Plus lent que SPI |

| Multi-maître natif | Open-drain → résistances pull-up nécessaires |

| Adressage → pas de SS_N | Protocole plus complexe |

| ACK/NACK pour vérification | Capacité du bus limitée (400 pF) |