Protocole UART

Maîtrisez le protocole UART (Universal Asynchronous Receiver/Transmitter) et son implémentation VHDL

Qu'est-ce que UART ?

UART (Universal Asynchronous Receiver/Transmitter) est un protocole série asynchrone : contrairement à SPI et I2C, il n'y a pas de signal d'horloge partagé entre émetteur et récepteur. La synchronisation se fait par un débit de communication prédéfini appelé baud rate (bits par seconde).

Ses caractéristiques principales :

- Asynchrone : pas d'horloge partagée

- Full-duplex : TX et RX sont des lignes indépendantes

- Point à point : 2 dispositifs uniquement (pas de bus multi-esclaves)

- Baud rate : les deux parties doivent être configurées au même débit

Signaux UART

| Signal | Description |

|---|---|

| TX | Transmission — données envoyées |

| RX | Réception — données reçues |

| GND | Masse commune (obligatoire) |

À l'état de repos, la ligne TX est au niveau haut (logique '1', appelé "mark").

Trame UART

Une trame UART standard (8N1 — 8 bits données, pas de parité, 1 bit stop) :

- Bit de Start : niveau bas pendant 1 période de bit — signale le début de la trame

- Bits de données : 5 à 9 bits, LSB en premier (convention standard)

- Bit de parité (optionnel) : paire, impaire ou aucune

- Bit(s) de Stop : niveau haut pendant 1 ou 2 périodes de bit — fin de trame

Baud Rate et diviseur d'horloge

Le baud rate détermine la durée d'un bit : T_bit = 1 / baud_rate

| Baud Rate | T_bit |

|---|---|

| 9600 bps | 104,2 µs |

| 115200 bps | 8,68 µs |

| 1 Mbps | 1 µs |

Pour générer le baud rate à partir d'une horloge système, on calcule un diviseur :

DIVISEUR = CLK_SYS / BAUD_RATE

Exemple : 100 MHz / 115200 ≈ 868Implémentation VHDL

L'émetteur UART utilise une machine à états avec 4 phases : IDLE, START, DATA et STOP. Un diviseur d'horloge (CLK_SYS / BAUD_RATE) génère le timing de chaque bit. Les données sont envoyées LSB en premier, conformément au standard.

Des exercices UART seront bientôt disponibles sur la plateforme pour mettre en pratique l'implémentation d'un émetteur et d'un récepteur UART complets.

Récepteur UART — Suréchantillonnage 16x

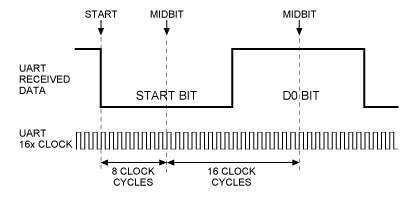

Le récepteur doit se synchroniser sur le bit de Start, puis échantillonner chaque bit au centre de sa période pour maximiser la robustesse au bruit.

La technique classique est le suréchantillonnage 16x : le diviseur de fréquence génère 16 ticks par période de bit. Le récepteur :

- Attend le front descendant du bit de Start

- Attend 8 ticks (demi-période) pour se placer au centre du bit de Start

- Vérifie que la ligne est bien bas (valide le Start)

- Tous les 16 ticks, échantillonne un bit de données

constant c_DIV16 : positive := g_CLK_HZ / (g_BAUD * 16);Points d'attention

- Même baud rate des deux côtés : une différence de plus de 3-5% provoque des erreurs de décodage

- Inversion logique : UART RS-232 utilise des niveaux ±12 V. Un MAX232 ou adaptateur est nécessaire pour interfacer avec du 3,3 V ou 5 V

- Pas de détection d'erreurs : sauf avec le bit de parité (optionnel) — les protocoles de niveau supérieur (ex : Modbus) ajoutent des checksums

- Niveau de repos : la ligne TX doit être haute au repos. Un TX déconnecté sera perçu comme un flux de données constant

Avantages et inconvénients

| Avantages | Inconvénients |

|---|---|

| Simple, 2 fils suffit | Point à point uniquement |

| Pas d'horloge partagée | Baud rate identique des deux côtés |

| Largement répandu | Pas de détection d'erreurs native |

| Distances plus longues (RS-232/485) | Pas de multi-maître |