Protocole Avalon

Découvrez le protocole Avalon d'Intel/Altera pour les interfaces mémoire et streaming dans les FPGA

Qu'est-ce que Avalon ?

Avalon est une famille de protocoles d'interface développée par Intel (anciennement Altera) pour leurs FPGA Cyclone, Arria et Stratix. Il est utilisé dans Platform Designer (anciennement Qsys) pour connecter des IPs dans un SoC FPGA.

La famille Avalon comprend plusieurs variantes :

- Avalon-MM (Memory Mapped) : accès registres et mémoires

- Avalon-ST (Streaming) : flux de données continu

- Avalon-Interrupt : signaux d'interruption

- Avalon-Clock : distribution d'horloge

- Avalon-Conduit : signaux personnalisés hors-protocole

Avalon-MM (Memory Mapped)

Signaux principaux

| Signal | Direction (Maître) | Description |

|---|---|---|

| address | Sortie | Adresse mot |

| read | Sortie | Demande de lecture |

| write | Sortie | Demande d'écriture |

| readdata | Entrée | Données lues (esclave → maître) |

| writedata | Sortie | Données écrites (maître → esclave) |

| byteenable | Sortie | Masque d'octets actifs |

| waitrequest | Entrée | L'esclave demande d'attendre |

| readdatavalid | Entrée | (pipeline) Les données lues sont valides |

Cycles de lecture et d'écriture Avalon-MM

Le maître doit maintenir read et address stables tant que waitrequest est haut.

Implémentation VHDL

Un esclave Avalon-MM zéro-latence est l'implémentation la plus simple : waitrequest est toujours bas, et les lectures/écritures s'exécutent en un seul cycle. L'esclave décode l'adresse pour accéder à un tableau de registres interne.

Des exercices Avalon seront bientôt disponibles sur la plateforme pour mettre en pratique l'implémentation d'un esclave Avalon-MM.

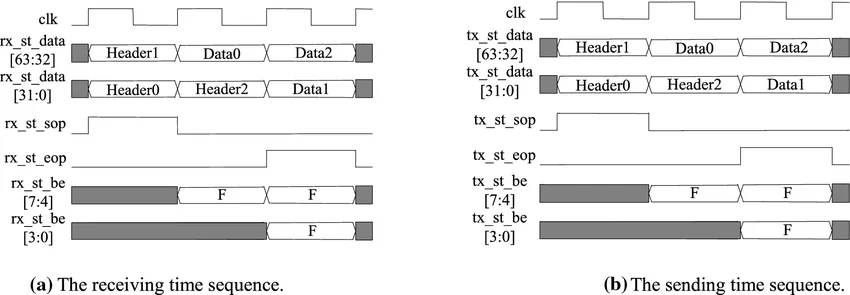

Avalon-ST (Streaming)

Avalon-ST est conçu pour les flux de données continus (audio, vidéo, réseau). Il utilise un handshake valid/ready similaire à AXI-Stream.

Signaux principaux

| Signal | Direction (Source) | Description |

|---|---|---|

| data | Sortie | Données du flux |

| valid | Sortie | Les données sont valides |

| ready | Entrée | Le récepteur peut accepter |

| startofpacket | Sortie | Premier beat d'un paquet |

| endofpacket | Sortie | Dernier beat d'un paquet |

| empty | Sortie | Nombre d'octets vides dans le dernier beat |

| error | Sortie | Erreur associée au beat |

Handshake valid/ready

Un transfert a lieu quand valid = '1' ET ready = '1' au même front d'horloge.

CLK : ___‾___‾___‾___‾___‾___‾

valid : |‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾|

ready : |‾‾‾‾‾|_____|‾‾‾‾‾‾‾|

data : | D0 | X | D1 | D2|

↑ ↑ ↑

transfert pause transfertsComparaison Avalon-MM vs AXI-Lite

| Critère | Avalon-MM | AXI-Lite |

|---|---|---|

| Standard | Intel/Altera | ARM (AMBA) |

| Canaux séparés | Non | Oui (5 canaux) |

| Mécanisme d'attente | waitrequest | handshake valid/ready |

| Burst natif | Oui | Non (AXI4 full) |

| Génération automatique | Platform Designer | Vivado IP Integrator |

| Usage typique | Cyclone, Arria, Stratix | Zynq, UltraScale |

Points d'attention

- Polarité du reset : Avalon utilise un reset actif haut (

reset = '1') — contrairement à beaucoup de designs VHDL qui préfèrent le reset actif bas - Latence de lecture : pour les esclaves avec des RAMs ou des calculs, utiliser

readdatavalidplutôt quewaitrequestpour indiquer que les données sont prêtes - Byteenable : si l'esclave ne supporte pas les accès partiels, ignorer byteenable et traiter tous les accès comme 32 bits

- Platform Designer : en pratique, les interfaces Avalon sont générées automatiquement par l'outil. Comprendre les signaux permet de créer des IPs custom correctement

Exemple : IP custom dans Platform Designer

# Déclaration de l'interface Avalon-MM dans le TCL de l'IP

add_interface s0 avalon slave

set_interface_property s0 addressUnits WORDS

add_interface_port s0 address address 2 Input

add_interface_port s0 read read 1 Input

add_interface_port s0 write write 1 Input

add_interface_port s0 readdata readdata 32 Output

add_interface_port s0 writedata writedata 32 Input

add_interface_port s0 waitrequest waitrequest 1 Output