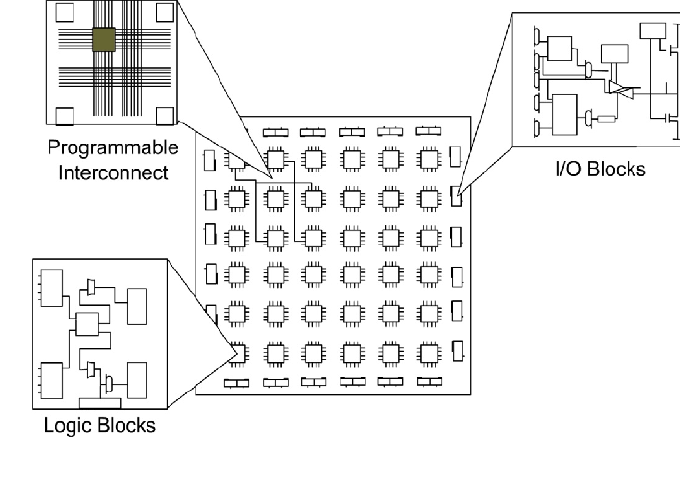

FPGA Internal Architecture

LUTs, flip-flops, block RAM, DSP, interconnects — the physical resources of a modern FPGA.

What is an FPGA?

An FPGA (Field-Programmable Gate Array) is an integrated circuit whose logic is reconfigurable after manufacturing. Unlike an ASIC (fixed circuit), an FPGA can be reprogrammed as many times as needed.

Main Resources

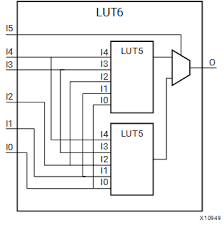

LUT — Look-Up Table

The basic building block of configurable logic. A LUT is a small memory that implements any logic function.

A LUT-6 (6 inputs, standard Xilinx 7-series) can implement any function of 6 variables → 2⁶ = 64 memory locations.

| Parameter | Xilinx 7-series | Intel Cyclone V |

|---|---|---|

| LUT | LUT-6 | LUT-6 (ALM) |

| LUTs / CLB | 8 | 10 / ALM |

| Typical count | 13k – 2M | 25k – 300k |

D Flip-Flop

Each LUT is paired with one or more D flip-flops. They store state between clock cycles.

A CLB (Configurable Logic Block) typically contains 8 LUTs + 16 flip-flops.

Carry Chain

CLBs have fast carry propagation chains, enabling high-performance adders and counters.

BRAM — Block RAM

On-chip memory embedded in the FPGA. Organized in fixed-size blocks (typically 18 kbits or 36 kbits).

-- Simple-port BRAM automatic inference

architecture rtl of bram_sp is

type t_mem is array(0 to 255) of std_logic_vector(7 downto 0);

signal r_mem : t_mem;

begin

process(i_clk)

begin

if rising_edge(i_clk) then

if i_we = '1' then

r_mem(to_integer(unsigned(i_addr))) <= i_data;

end if;

o_data <= r_mem(to_integer(unsigned(i_addr)));

end if;

end process;

end architecture rtl;| Parameter | Typical Value |

|---|---|

| Block size | 18 kbits or 36 kbits |

| Block count | 100 – 2000 |

| Modes | Simple port, dual port, true dual port |

| Latency | 1 cycle |

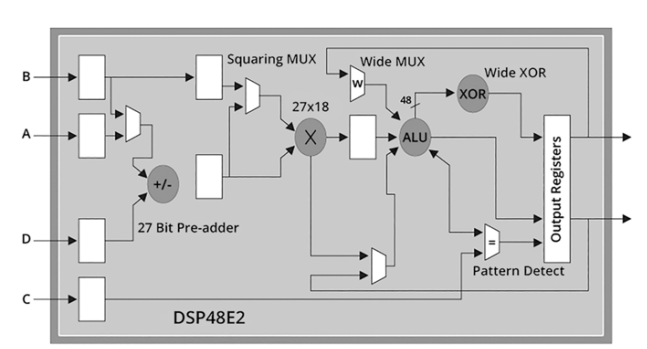

DSP — Digital Signal Processing

Dedicated hardware blocks for multiplications and MAC (Multiply-Accumulate) operations.

A DSP48 block (Xilinx) computes: P = A ×-B + C in 1 cycle at high frequency.

Typical usage:

- Digital filters (FIR, IIR)

- Correlators, FFT

- Image processing units

The synthesizer automatically infers DSPs from your VHDL if the structure matches.

I/O — Input/Output

FPGA pins are configurable I/Os:

| Standard | Usage |

|---|---|

| LVCMOS 3.3V / 1.8V | General GPIO |

| LVDS | High-speed differential |

| SSTL | DDR memories |

| SERDES | Very high speed (HDMI, PCIe) |

-- Placement constraint (Xilinx XDC)

set_property PACKAGE_PIN W5 [get_ports o_led]

set_property IOSTANDARD LVCMOS33 [get_ports o_led]Interconnects

Resources are connected through a programmable interconnect network. This is often the limiting factor for maximum frequency.

The synthesizer chooses routing paths — which is why the same VHDL description can have different performance depending on the FPGA or constraints.

Common FPGA Families

| Manufacturer | Family | Target |

|---|---|---|

| Xilinx (AMD) | Artix-7, Kintex-7 | Mid-range |

| Xilinx (AMD) | Zynq-7000 | SoC (ARM + FPGA) |

| Xilinx (AMD) | Virtex Ultrascale+ | High performance |

| Intel (Altera) | Cyclone V / 10 | Low-cost |

| Intel (Altera) | Arria 10 | Mid-range |

| Lattice | ECP5 | Ultra low-power |

| Gowin | GW1N | Low cost, hobbyists |