Static Timing Analysis (STA)

Understanding setup time, hold time, critical paths and slack calculation in FPGA design.

What is STA?

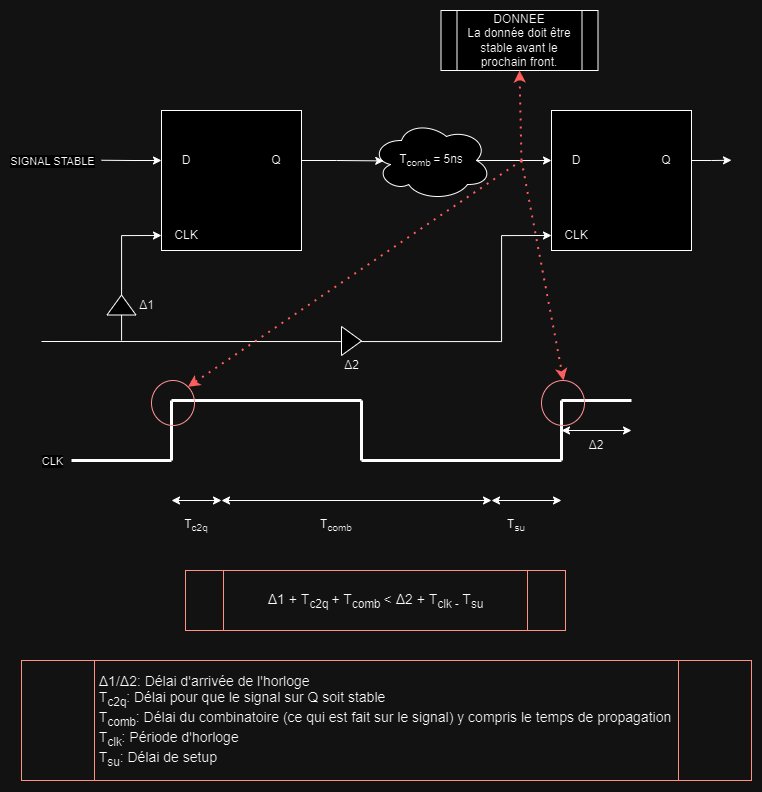

Static Timing Analysis is a method used to evaluate the timing behavior of a circuit without running a full simulation. It examines critical paths — paths where signals must meet strict timing constraints to ensure correct operation.

These constraints include:

- Clock delays

- Signal propagation times

- Synchronization parameters (setup, hold)

STA allows you to detect timing violations before programming the FPGA.

Setup Time and Hold Time

Setup Time

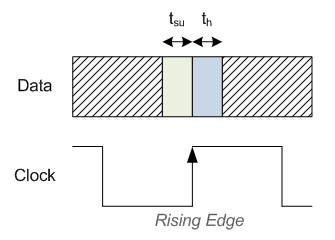

The setup time is how long data must be stable before the clock edge to be correctly captured by a flip-flop.

If data arrives too late (setup violation), the flip-flop may capture an incorrect or undefined value.

Hold Time

The hold time is how long data must remain stable after the clock edge to ensure correct capture.

If data changes too soon after the edge (hold violation), the flip-flop may capture an erroneous value.

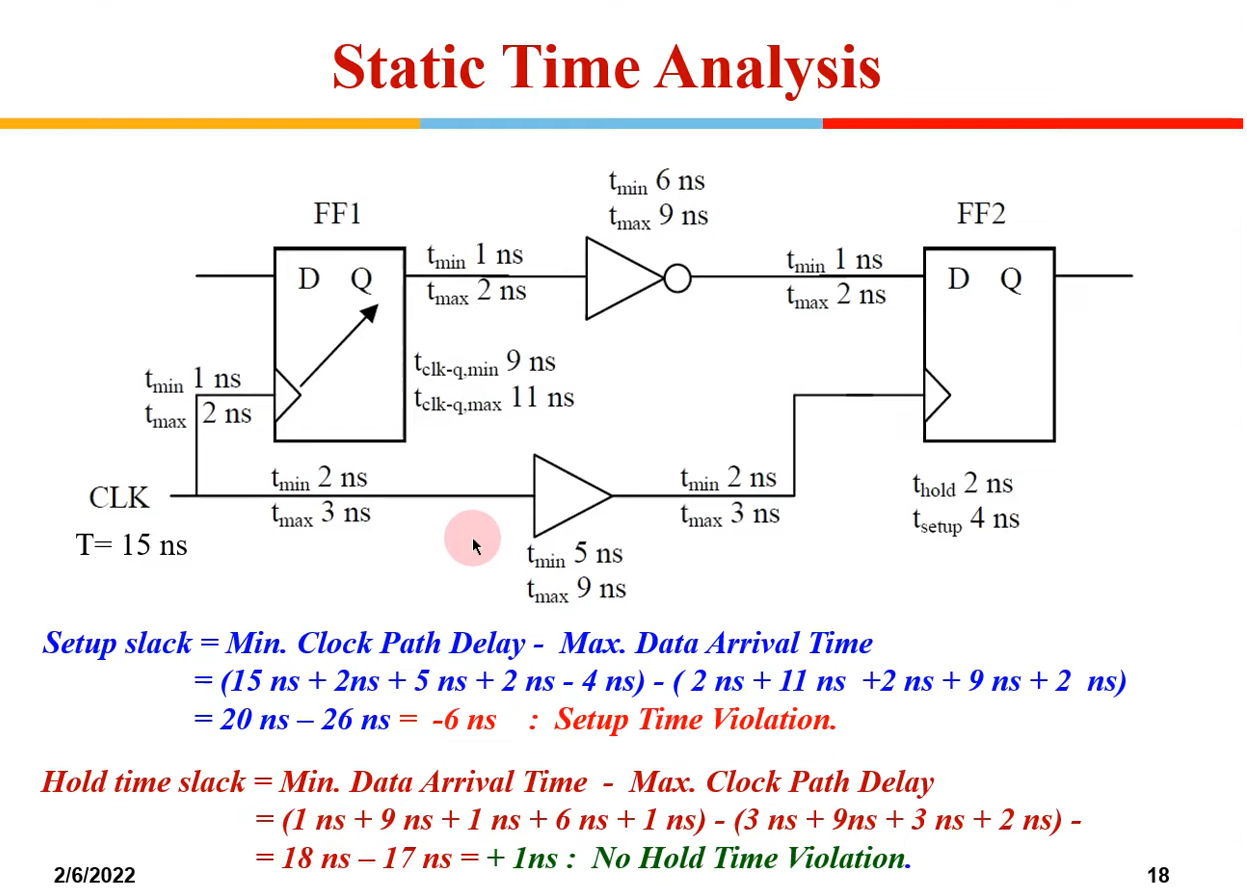

Slack Calculation

Slack is the calculated timing margin. Positive slack means timing is met; negative slack means a violation.

Setup Slack

Setup Slack = Tdata,max − Tclock,min

Subtract the sum of minimum clock path delays from the sum of maximum data arrival times.

In the example above: −6 ns → setup violation. Reduce the clock frequency or optimize the path.

Hold Slack

Hold Slack = Tdata,min − Tclock,max

Subtract the sum of maximum clock path delays from the sum of minimum data arrival times.

In the example above: +1 ns → no violation.

What Modern Tools Do

Tools like Vivado automatically compute all these margins after the implementation (place & route) phase. The timing report shows:

| Report | Description |

|---|---|

| WNS (Worst Negative Slack) | Worst setup margin — must be ≥ 0 |

| WHS (Worst Hold Slack) | Worst hold margin — must be ≥ 0 |

| TNS (Total Negative Slack) | Sum of all setup violations |

| THS (Total Hold Slack) | Sum of all hold violations |

Knowing how to read and interpret these reports is important, even though Vivado generates them automatically. An uncorrected timing error can cause random behavior on the FPGA.