AXI Protocol

The AXI (Advanced eXtensible Interface) protocol by ARM: write/read channels, burst transfers and handshake.

What is AXI?

The AXI (Advanced eXtensible Interface) protocol is an interconnect protocol developed by ARM for its AMBA architectures. It standardizes high-performance communication between hardware components in a SoC (System on Chip).

Its two key strengths:

- Performance: designed for high-frequency data exchange

- Handshake: reliable synchronization via independent

VALID/READYsignals

AXI is split into two parts: addresses and data. This requires a significant number of signals.

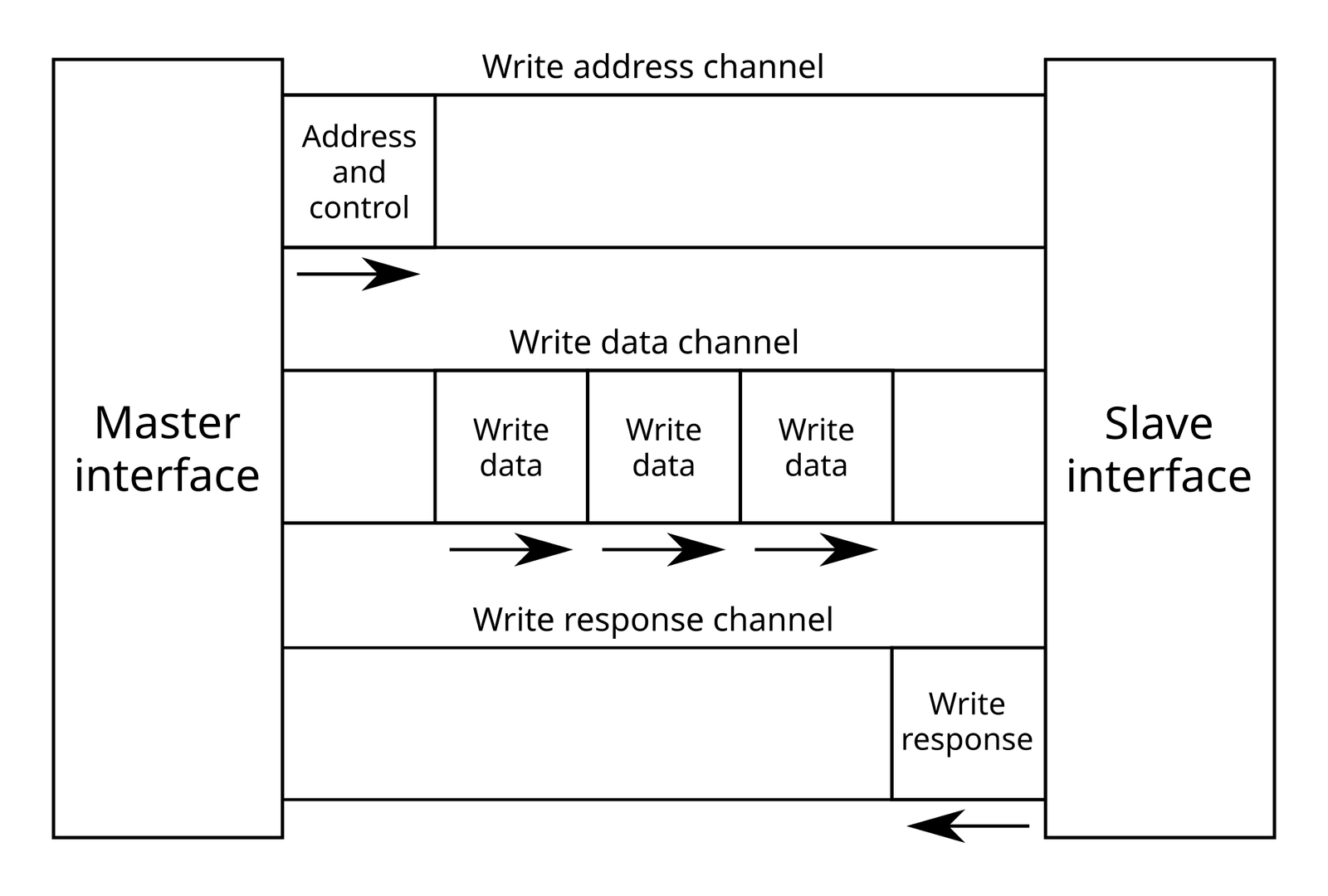

Write

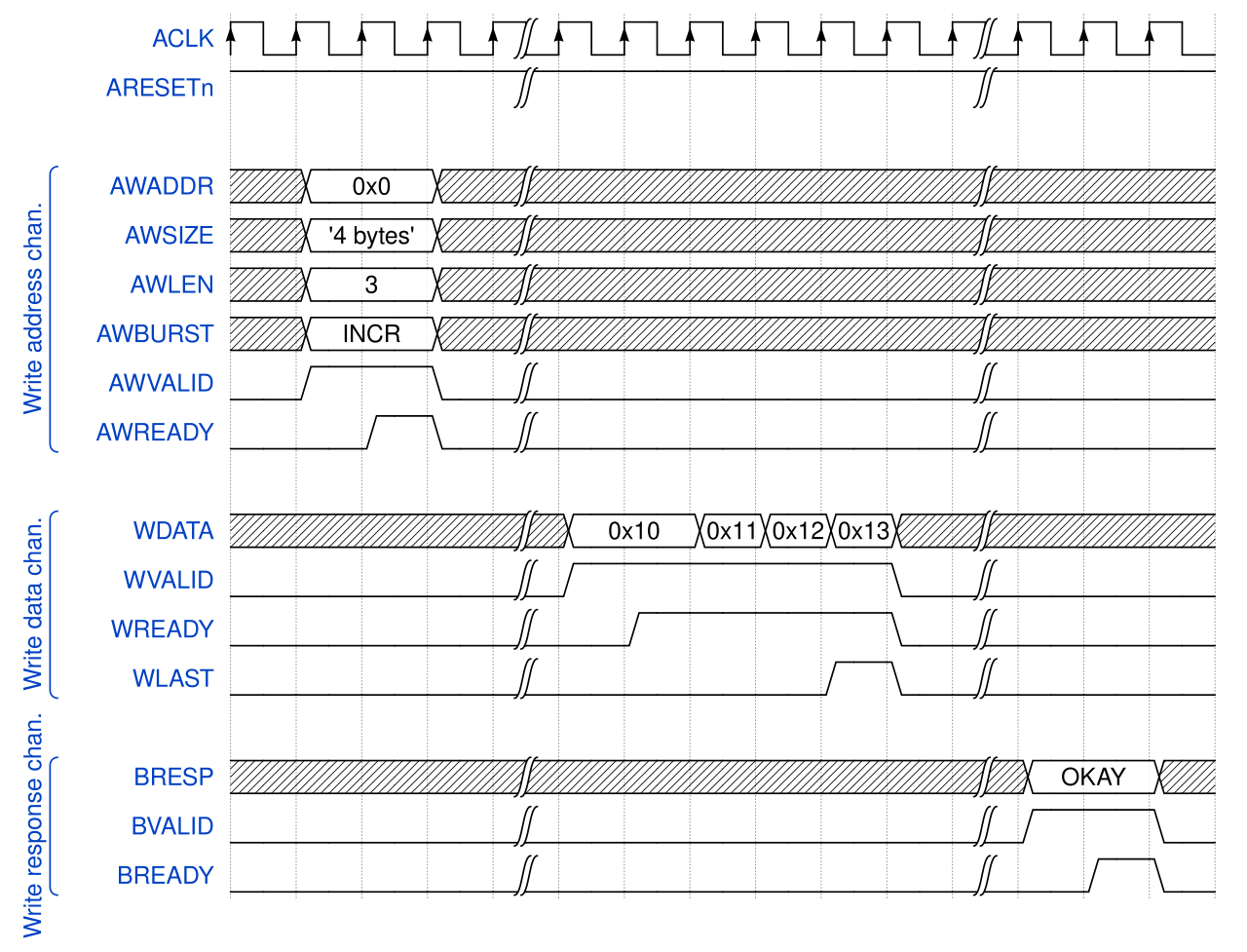

A write transaction requires 13 signals across three channels: Write Address (AW), Write Data (W), and Write Response (B).

Writes can be done with or without burst. Burst mode sends a single start address followed by successive data beats — saving time when addresses are contiguous.

Write transaction sequence:

- Place the address on AWADDR, set data width (AWSIZE) and transaction length (AWLEN).

- Assert AWVALID in parallel and wait for AWREADY from the slave.

- Wait for WREADY and send data in burst with WVALID asserted.

- Assert WLAST on the last data beat.

- Check the response on BRESP (expected:

OKAY).

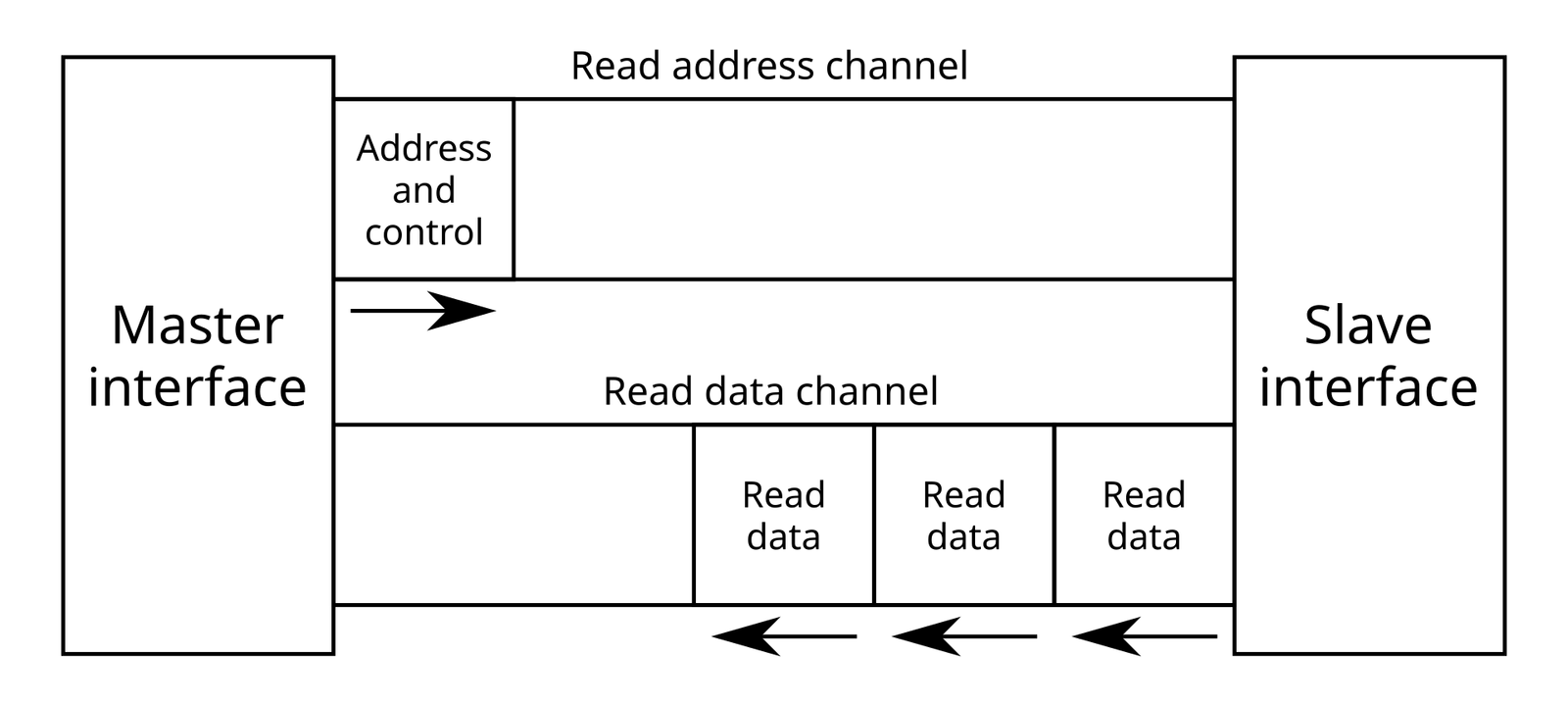

Read

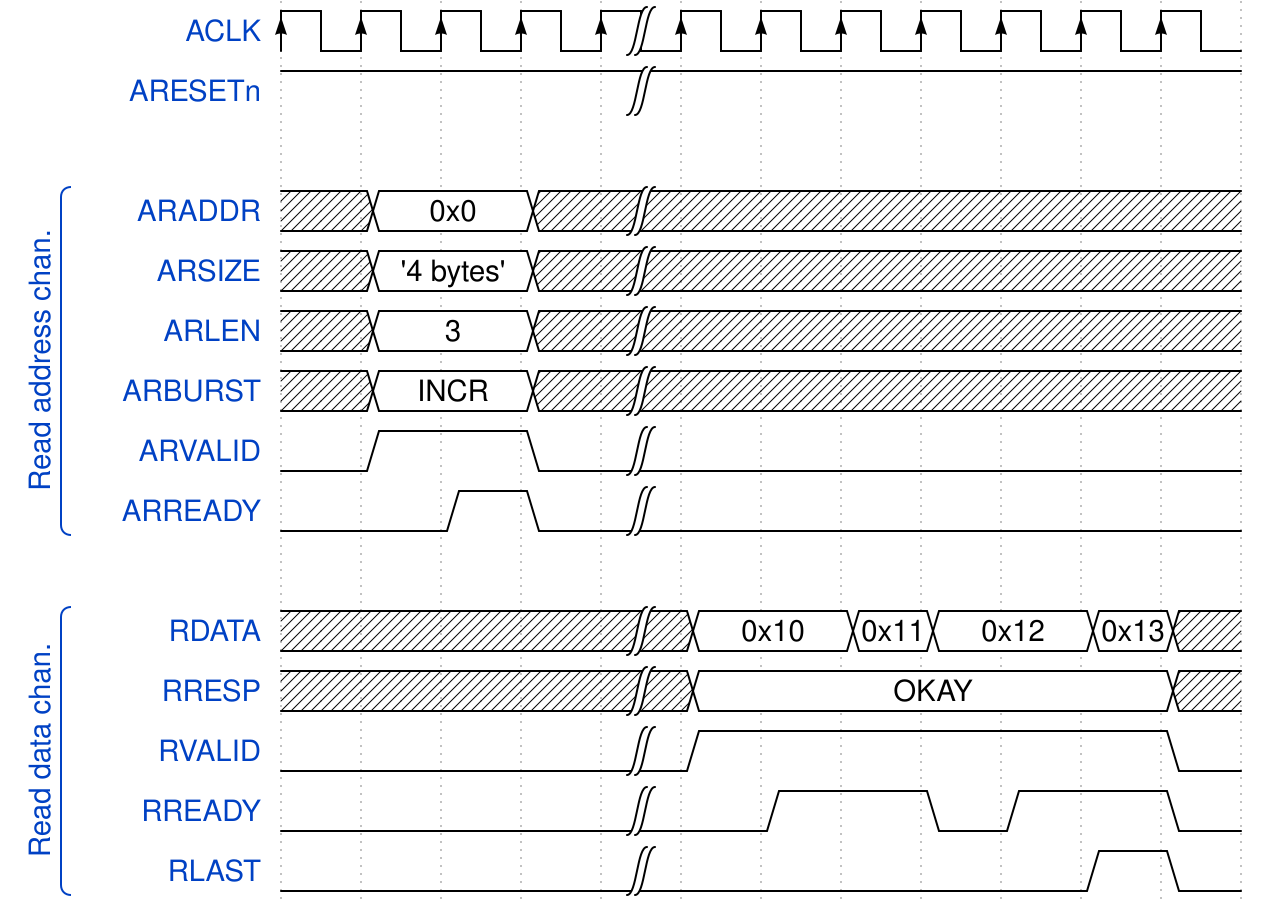

A read transaction requires 11 signals across two channels: Read Address (AR) and Read Data (R).

Read transaction sequence:

- Place the address on ARADDR, set ARSIZE and ARLEN.

- Assert ARVALID in parallel and wait for ARREADY from the slave.

- Wait for RVALID and read data in burst.

- Watch RLAST to detect the last data beat.

- Check the response on RRESP (expected:

OKAY).

Signal Summary

| Channel | Key Signals | Direction |

|---|---|---|

| AW (Write Address) | AWADDR, AWLEN, AWSIZE, AWVALID, AWREADY | Master → Slave |

| W (Write Data) | WDATA, WSTRB, WLAST, WVALID, WREADY | Master → Slave |

| B (Write Response) | BRESP, BVALID, BREADY | Slave → Master |

| AR (Read Address) | ARADDR, ARLEN, ARSIZE, ARVALID, ARREADY | Master → Slave |

| R (Read Data) | RDATA, RLAST, RRESP, RVALID, RREADY | Slave → Master |

For a simplified version (no burst, no complex address management), see the AXI-Lite Protocol course.