AXI-Lite Protocol

AXI-Lite: the simplified AXI variant for configuration registers and control interfaces.

What is AXI-Lite?

AXI-Lite is a simplified version of the AXI protocol developed by ARM as part of the AMBA architecture. It is particularly suited for control and configuration communications within a SoC.

Unlike full AXI4, AXI-Lite:

- Does not support burst (one data beat per transaction)

- Has a fixed data width

- Uses fewer signals

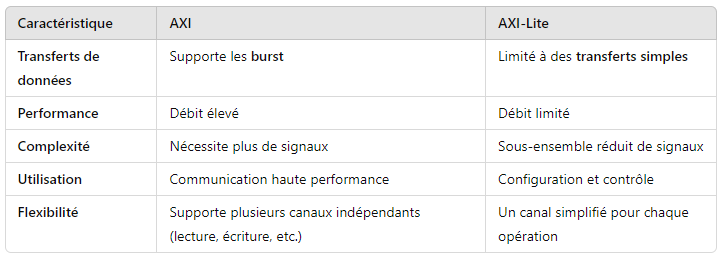

Comparison with AXI

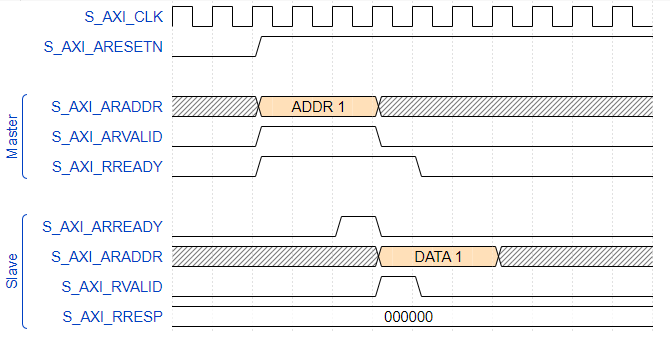

Read

Only 7 signals are needed for a complete read transaction.

Sequence:

- Master waits for RREADY from the Slave (Slave is ready to respond).

- Master places the address on ARADDR and asserts ARVALID.

- Slave asserts ARREADY, indicating it accepts the address.

- Both Master and Slave deassert ARVALID and ARREADY.

- Slave sends data on RDATA and asserts RVALID (RRESP may indicate an error).

- On the next rising clock edge (both RREADY and RVALID asserted), the transaction completes. Slave deasserts RVALID.

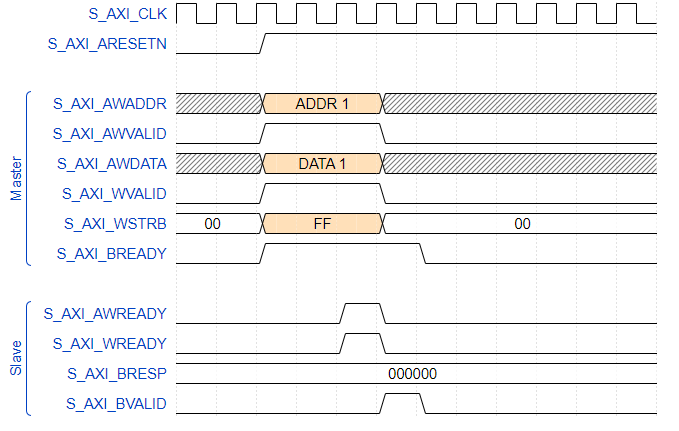

Write

Write transactions require 10 signals.

Sequence:

- Master places the address on AWADDR.

- Master asserts AWVALID and waits for AWREADY from the Slave.

- Master places data on WDATA (and byte mask on WSTRB).

- Master asserts WVALID and waits for WREADY from the Slave.

- Master waits for BVALID from the Slave.

- Slave provides the response on BRESP (

OKAYif successful). - Master asserts BREADY to acknowledge the response.

Signal Summary

| Channel | Signals | Count |

|---|---|---|

| Write Address | AWADDR, AWVALID, AWREADY | 3 |

| Write Data | WDATA, WSTRB, WVALID, WREADY | 4 |

| Write Response | BRESP, BVALID, BREADY | 3 |

| Read Address | ARADDR, ARVALID, ARREADY | 3 |

| Read Data | RDATA, RRESP, RVALID, RREADY | 4 |

AXI-Lite is the protocol of choice for configuration registers and simple peripherals in a Zynq SoC.