Avalon Protocol

Discover Intel/Altera's Avalon protocol for memory-mapped and streaming interfaces in FPGAs

What is Avalon?

Avalon is a family of interface protocols developed by Intel (formerly Altera) for their Cyclone, Arria, and Stratix FPGAs. It is used in Platform Designer (formerly Qsys) to connect IPs within an FPGA SoC.

The Avalon family includes several variants:

- Avalon-MM (Memory Mapped): register and memory access

- Avalon-ST (Streaming): continuous data stream

- Avalon-Interrupt: interrupt signals

- Avalon-Clock: clock distribution

- Avalon-Conduit: custom out-of-band signals

Avalon-MM (Memory Mapped)

Main Signals

| Signal | Direction (Master) | Description |

|---|---|---|

| address | Output | Word address |

| read | Output | Read request |

| write | Output | Write request |

| readdata | Input | Read data (slave → master) |

| writedata | Output | Write data (master → slave) |

| byteenable | Output | Active byte mask |

| waitrequest | Input | Slave requests a wait cycle |

| readdatavalid | Input | (pipeline) Read data is valid |

Avalon-MM Read and Write Cycles

The master must hold read and address stable while waitrequest is high.

VHDL Implementation

A zero-latency Avalon-MM slave is the simplest implementation: waitrequest is always low, and reads/writes execute in a single cycle. The slave decodes the address to access an internal register array.

Avalon exercises will be available soon on the platform to practice implementing an Avalon-MM slave.

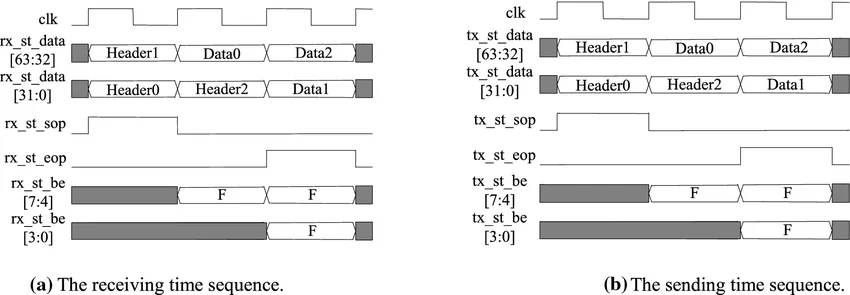

Avalon-ST (Streaming)

Avalon-ST is designed for continuous data streams (audio, video, network). It uses a valid/ready handshake similar to AXI-Stream.

Main Signals

| Signal | Direction (Source) | Description |

|---|---|---|

| data | Output | Stream data |

| valid | Output | Data is valid |

| ready | Input | Sink can accept data |

| startofpacket | Output | First beat of a packet |

| endofpacket | Output | Last beat of a packet |

| empty | Output | Number of empty bytes in the last beat |

| error | Output | Error associated with the beat |

valid/ready Handshake

A transfer occurs when valid = '1' AND ready = '1' on the same clock edge.

CLK : ___‾___‾___‾___‾___‾___‾

valid : |‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾‾|

ready : |‾‾‾‾‾|_____|‾‾‾‾‾‾‾|

data : | D0 | X | D1 | D2|

↑ ↑ ↑

transfer pause transfersAvalon-MM vs AXI-Lite Comparison

| Criterion | Avalon-MM | AXI-Lite |

|---|---|---|

| Standard | Intel/Altera | ARM (AMBA) |

| Separate channels | No | Yes (5 channels) |

| Wait mechanism | waitrequest | valid/ready handshake |

| Native burst | Yes | No (AXI4 full) |

| Auto-generation | Platform Designer | Vivado IP Integrator |

| Typical use | Cyclone, Arria, Stratix | Zynq, UltraScale |

Key Points

- Reset polarity: Avalon uses active-high reset (

reset = '1') — unlike many VHDL designs that prefer active-low reset - Read latency: for slaves with RAMs or computations, use

readdatavalidrather thanwaitrequestto indicate data is ready - Byteenable: if the slave doesn't support partial accesses, ignore byteenable and treat all accesses as 32-bit

- Platform Designer: in practice, Avalon interfaces are auto-generated by the tool. Understanding the signals enables creating custom IPs correctly

Example: Custom IP in Platform Designer

# Declaring the Avalon-MM interface in the IP TCL file

add_interface s0 avalon slave

set_interface_property s0 addressUnits WORDS

add_interface_port s0 address address 2 Input

add_interface_port s0 read read 1 Input

add_interface_port s0 write write 1 Input

add_interface_port s0 readdata readdata 32 Output

add_interface_port s0 writedata writedata 32 Input

add_interface_port s0 waitrequest waitrequest 1 Output