Introduction to VHDL

What is VHDL, its history, and why use it for FPGAs?

What is VHDL?

VHDL (VHSIC Hardware Description Language) is an IEEE-standardized hardware description language (HDL). It allows describing the behavior and structure of digital circuits.

VHSIC = Very High Speed Integrated Circuits — a US military research program from the 1980s.

VHDL is used to:

- Model and simulate digital circuits

- Synthesize code into real hardware (FPGA, ASIC)

- Document and verify the architecture of a digital system

History

| Year | Event |

|---|---|

| 1983 | Created by the DOD (US Department of Defense) |

| 1987 | First standardization IEEE 1076-1987 |

| 1993 | Major revision IEEE 1076-1993 (VHDL-93) |

| 2008 | VHDL-2008: added unsigned types, IEEE numeric_std |

| 2019 | VHDL-2019: latest current revision |

The most widely used version in industry is VHDL-93 / VHDL-2008.

VHDL vs Verilog

These two languages dominate the market. Here is a comparison:

| Criterion | VHDL | Verilog |

|---|---|---|

| Syntax | Verbose, strongly typed | Compact, C-like |

| Popularity | Europe, defense, aerospace | USA, Asia, semiconductors |

| Typing | Strict (strongly typed) | Permissive |

| Standard | IEEE 1076 | IEEE 1364 / 1800 (SystemVerilog) |

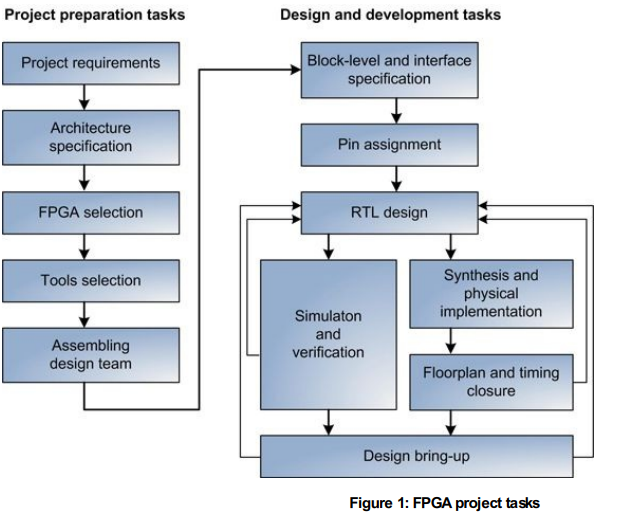

FPGA Design Flow

- Writing: you describe the behavior in VHDL

- Simulation: functional verification (testbench)

- Synthesis: transformation into a netlist of logic gates

- Implementation: placement onto FPGA physical resources

- Programming: loading the bitstream onto the chip

First VHDL Preview

Here is the minimal structure of a VHDL file:

library IEEE;

use IEEE.STD_LOGIC_1164.ALL;

entity my_circuit is

port (

i_a : in std_logic;

i_b : in std_logic;

o_y : out std_logic

);

end entity my_circuit;

architecture rtl of my_circuit is

begin

o_y <= i_a AND i_b;

end architecture rtl;This code describes a simple AND gate with two inputs. We will cover each part in detail in the next courses.

Key Points to Remember

- VHDL describes hardware, not a sequential algorithm

- Everything in the architecture executes in parallel

- VHDL is strongly typed: types must match exactly

- Simulation and synthesis do not have the same constraints