Combinational and Sequential Logic

The fundamental distinction between combinational logic (no memory) and sequential logic (clocked).

Two Types of Digital Logic

In digital design, every circuit belongs to one of two categories:

| Combinational Logic | Sequential Logic | |

|---|---|---|

| Memory | No | Yes (flip-flops) |

| Depends on past | No | Yes |

| Clock | Not needed | Essential |

| Examples | Multiplexer, adder | Register, counter, FSM |

Combinational Logic

The output depends only on the current inputs. No internal state.

architecture rtl of mux2 is

begin

-- Concurrent assignment: immediate, combinational

o_y <= i_a when i_sel = '0' else i_b;

end architecture rtl;Characteristics

- No clock needed

- Instantaneous response (in practice: propagation delay)

- In synthesis: produces LUTs (Look-Up Tables)

Sequential Logic

The output depends on the inputs and the past state. It is synchronized on a clock.

architecture rtl of register_8 is

signal r_data : std_logic_vector(7 downto 0);

begin

process(i_clk)

begin

if rising_edge(i_clk) then

if i_rst = '1' then

r_data <= (others => '0');

else

r_data <= i_data;

end if;

end if;

end process;

o_data <= r_data;

end architecture rtl;Characteristics

- Synchronized on the rising edge (

rising_edge) or falling edge (falling_edge) - In synthesis: produces D flip-flops

- The

r_prefix indicates a registered signal (see course 07)

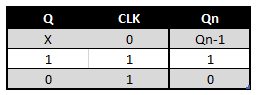

The D Flip-Flop — Building Block

The D flip-flop is the fundamental memory element:

- On each rising edge of CLK: Q takes the value of D

- Between edges: Q retains its previous value

process(i_clk)

begin

if rising_edge(i_clk) then

r_q <= i_d; -- simple D flip-flop

end if;

end process;Synchronous vs Asynchronous Reset

Synchronous Reset (recommended for FPGA)

process(i_clk)

begin

if rising_edge(i_clk) then

if i_rst = '1' then

r_q <= '0'; -- reset on the clock edge

else

r_q <= i_d;

end if;

end if;

end process;Asynchronous Reset

process(i_clk, i_rst)

begin

if i_rst = '1' then

r_q <= '0'; -- immediate reset, no clock edge required

elsif rising_edge(i_clk) then

r_q <= i_d;

end if;

end process;On FPGAs, synchronous reset is generally preferred because it uses the flip-flop resources more efficiently. Unless there is a specific constraint, use synchronous reset.

Sensitivity List Rules

For a combinational process: list all signals read in the process.

-- Combinational: i_a, i_b, i_sel in the list

process(i_a, i_b, i_sel)

begin

if i_sel = '0' then

w_y <= i_a;

else

w_y <= i_b;

end if;

end process;For a sequential process: only the clock (and asynchronous reset if used).

-- Sequential: only i_clk

process(i_clk)

begin

if rising_edge(i_clk) then

r_q <= i_d;

end if;

end process;VHDL-2008 introduces

process(all)which automatically captures all signals. Convenient but check tool compatibility.